AD7280A Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

производитель

AD7280A Datasheet PDF : 48 Pages

| |||

AD7280A

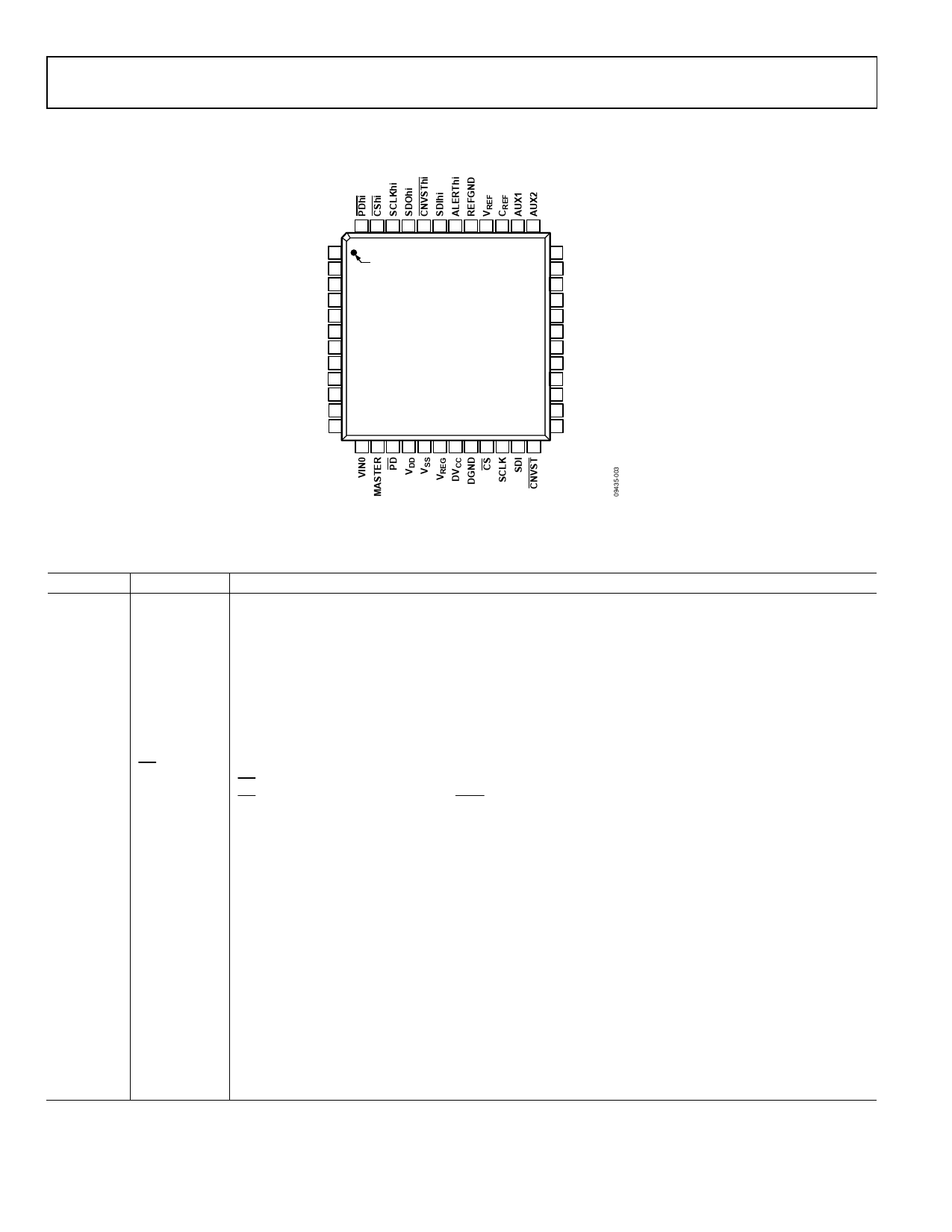

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

48 47 46 45 44 43 42 41 40 39 38 37

VIN6 1

CB6 2

VIN5 3

CB5 4

VIN4 5

CB4 6

VIN3 7

CB3 8

VIN2 9

CB2 10

VIN1 11

CB1 12

PIN 1

AD7280A

TOP VIEW

(Not to Scale)

36 AUX3

35 AUX4

34 AUX5

33 AUX6

32 AUXTERM

31 AGND

30 AVCC

29 VDRIVE

28 ALERTlo

27 ALERT

26 SDO

25 SDOlo

13 14 15 16 17 18 19 20 21 22 23 24

Figure 3. Pin Configuration

Table 6. Pin Function Descriptions

Pin No.

Mnemonic Description

1, 3, 5, 7, 9, VIN6 to VIN0

11, 13

Analog Input 6 to Analog Input 0. VIN0 should be connected to the base of the series-connected battery cells.

VIN1 should be connected to the top of Cell 1, VIN2 should be connected to the top of Cell 2, and so on (see

Figure 28 and Figure 29).

2, 4, 6, 8,

10, 12

CB6 to CB1

Cell Balance Output 6 to Cell Balance Output 1. These pins provide a voltage output that can be used to supply

the gate drive of an external cell balancing transistor. Each CBx output provides a 0 V or 5 V voltage output

referenced to the absolute amplitude of the negative terminal of the battery cell that is being balanced.

14

MASTER

Voltage Input. Connect the MASTER pin of the AD7280A that is connected directly to the DSP/microprocessor

to the VDD supply pin through a 10 kΩ resistor. In an application with two or more AD7280As in a daisy chain,

the MASTER pins of the remaining AD7280As in the daisy chain should be tied to their respective VSS supply

pins through 10 kΩ resistors.

15

PD

Power-Down Input. This input is used to power down the AD7280A. When the AD7280A acts as a master, the

PD input is supplied from the DSP/microprocessor. When the AD7280A acts as a slave in a daisy chain, the

PD input should be connected to the PDhi output of the AD7280A immediately below it in potential in the

daisy chain.

16

VDD

Positive Power Supply Voltage for the High Voltage Analog Input Structure of the AD7280A. The supply must be

greater than the minimum voltage of 8 V. VDD can be supplied directly from the cell with the highest potential

of the four, five, or six cell battery stacks that the AD7280A is monitoring. The maximum voltage that should

be applied between VDD and VSS is 30 V. Place 10 μF and 100 nF decoupling capacitors on the VDD pin.

17

VSS

Negative Power Supply Voltage for the High Voltage Analog Input Structure of the AD7280A. This input should

be at the same potential as the AGND/DGND voltage.

18

VREG

Analog Voltage Output, 5.2 V. The internally generated VREG voltage, which provides the supply voltage for

the ADC core, is available on this pin for use external to the AD7280A. Place 1 μF and 100 nF decoupling

capacitors on the VREG pin.

19

DVCC

Digital Supply Voltage, 4.9 V to 5.5 V. The DVCC and AVCC voltages should ideally be at the same potential.

For best performance, it is recommended that the DVCC and AVCC pins be shorted together to ensure that

the voltage difference between them never exceeds 0.3 V, even on a transient basis. This supply should be

decoupled to DGND. Place 100 nF decoupling capacitors on the DVCC pin. The DVCC supply pin should be

connected to the VREG output.

20

DGND

Digital Ground. Ground reference point for all digital circuitry on the AD7280A. The DGND and AGND voltages

should ideally be at the same potential and must not be more than 0.3 V apart, even on a transient basis.

Rev. 0 | Page 8 of 48