78Q2133 Просмотр технического описания (PDF) - Unspecified

Номер в каталоге

Компоненты Описание

производитель

78Q2133 Datasheet PDF : 42 Pages

| |||

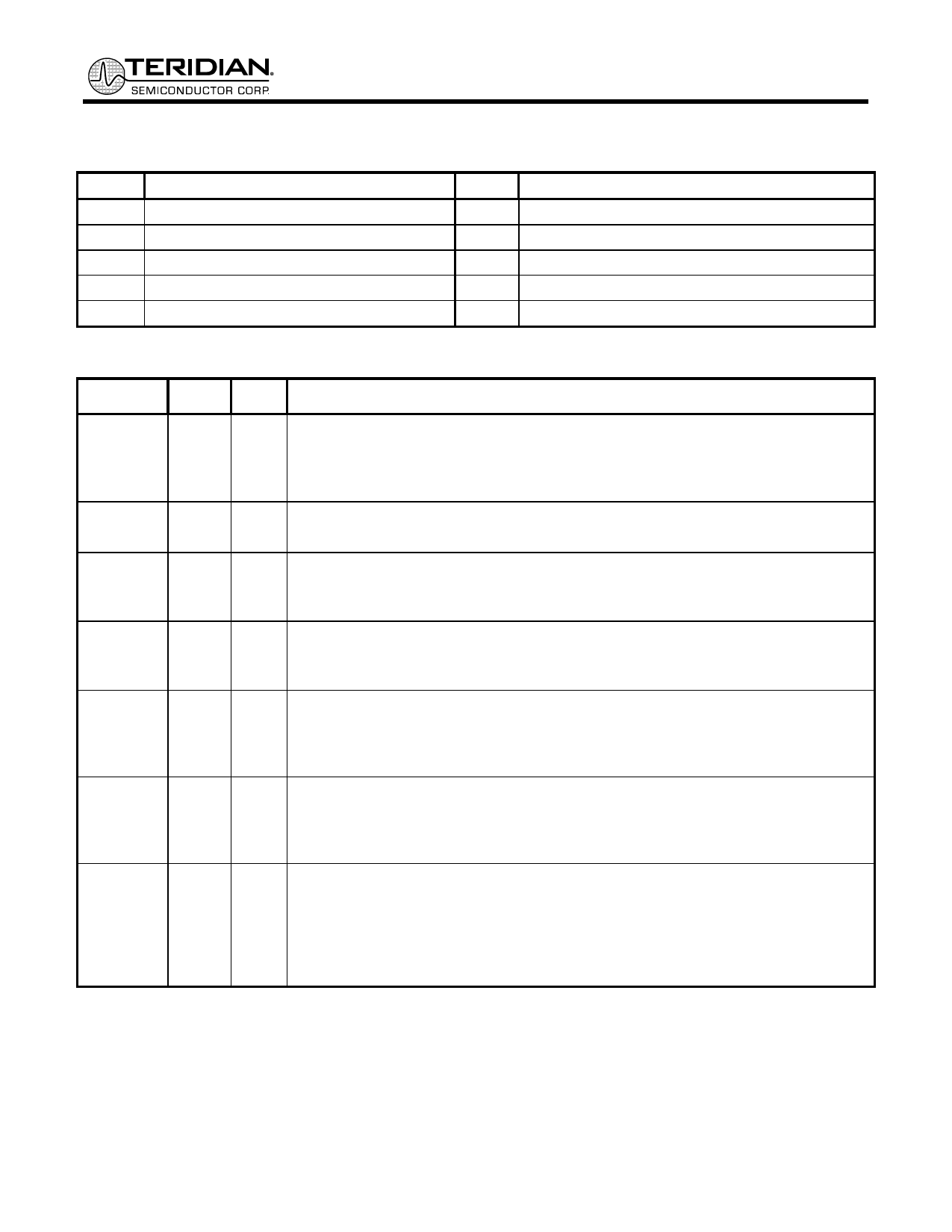

PIN DESCRIPTION

LEGEND

TYPE DESCRIPTION

A Analog Pin

CIU TTL-level Input w/ Pull-up

CIS TTL-level Input w/ Schmitt Trigger

CO CMOS Output

S Supply

78Q2123/78Q2133 MicroPHY™

10/100BASE-TX Transceiver

TYPE

CI

CIO

COZ

DESCRIPTION

TTL-level Input

TTL-compatible Bi-directional Pin

Tristate-able CMOS output

G Ground

MII (MEDIA INDEPENDENT INTERFACE)

SIGNAL PIN TYPE DESCRIPTION

TX_CLK

TX_EN

TXD[3:0]

TX_ER

CRS

COL

RX_CLK

15

COZ TRANSMIT CLOCK: TX_CLK is a continuous clock, which provides a timing

reference for the TX_EN, TX_ER and TXD[3:0] signals from the MAC. The clock

frequency is 25MHz in 100BASE-TX mode and 2.5MHz in 10BASE-T mode. This

pin is tri-stated in isolate mode and the TXHIM mode.

16

CI

TRANSMIT ENABLE: TX_EN is asserted by the MAC to indicate that valid data for

transmission is present on the TXD[3:0] pins.

[20:17] CI

TRANSMIT DATA: TXD[3:0] receives data from the MAC for transmission on a

nibble basis. This data is captured on the rising edge of TX_CLK when TX_EN is

high.

14

CI

TRANSMIT ERROR: TX_ER is asserted high by the MAC to request that an error

code-group be transmitted when TX_EN is high. In PCS bypass mode, this pin

becomes the MSB of the transmit 5-bit code group.

22

COZ CARRIER SENSE: When the 78Q2123/78Q2133 are not in repeater mode, CRS is

high whenever a non-idle condition exists on either the transmitter or the receiver.

In repeater mode, CRS is only active when a non-idle condition exists on the

receiver. This pin is tri-stated in isolate mode.

21

COZ COLLISION: COL is asserted high when a collision has been detected on the

media. In 10BASE-T mode COL is also used for the SQE test function. This pin is

tri-stated in isolate mode. During half duplex operation, the rising edge of COL will

occasionally occur upon the rising edge of TX_CLK.

12

COZ RECEIVE CLOCK: RX_CLK is a continuous clock, which provides a timing

reference to the MAC for the RX_DV, RX_ER and RXD[3:0] signals. The clock

frequency is 25MHz in 100BASE-TX mode and 2.5MHz in 10BASE-T mode. To

reduce power consumption in 100BASE-TX mode, the 78Q2123/78Q2133 provide

an optional mode, enabled through MR16.0, in which RX_CLK is held inactive (low)

when no receive data is detected. This pin is tri-stated in isolate mode.

Page: 7 of 42

© 2009 Teridian Semiconductor Corporation

Rev 1.5