EN5394QI Просмотр технического описания (PDF) - Altera Corporation

Номер в каталоге

Компоненты Описание

производитель

EN5394QI

EN5394QI Datasheet PDF : 19 Pages

| |||

EN5394QI

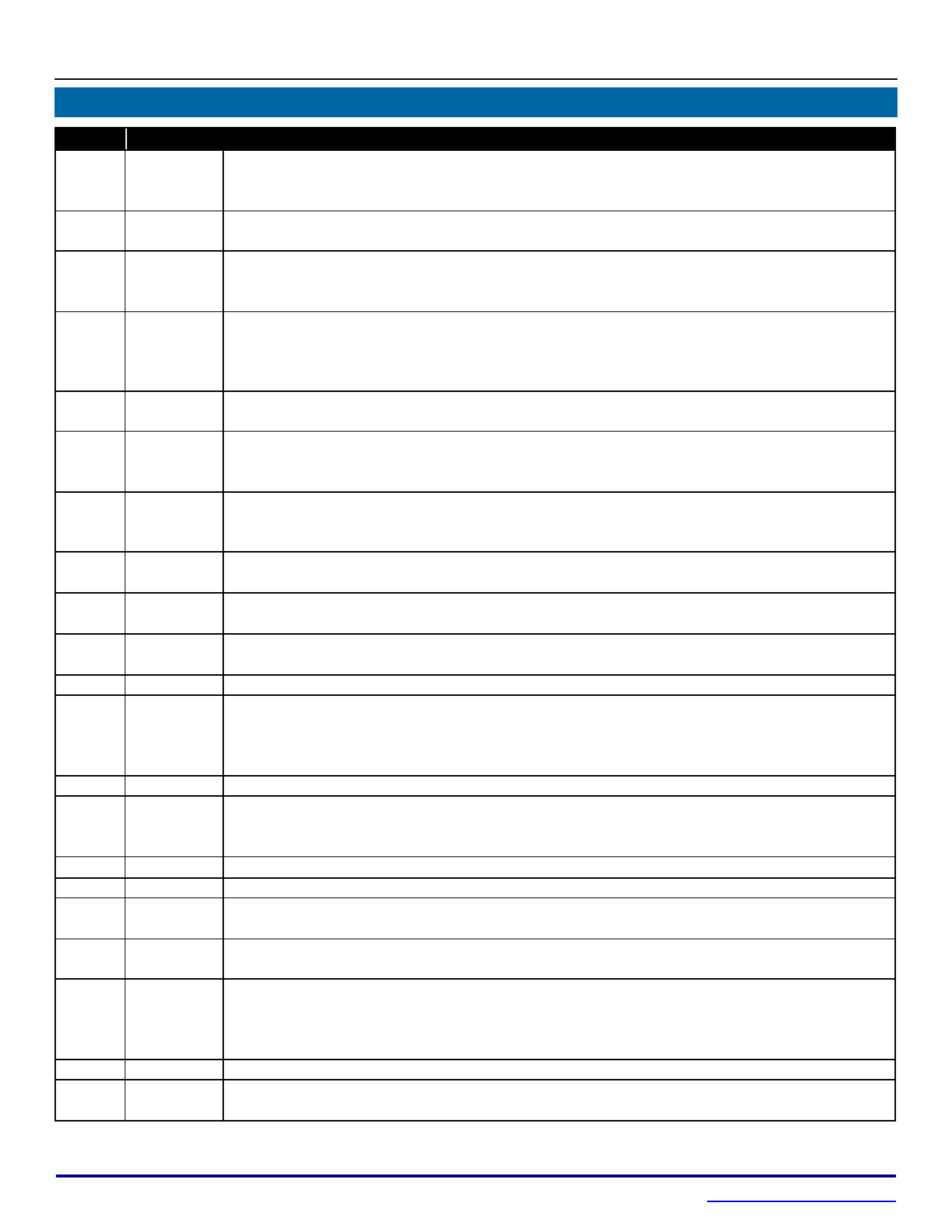

Pin Descriptions

PIN

1-4,

27-33,

64-68

5-13

14-24,

44-47

25-26

34-43

48

49

50

51

52

53

54

55

56

57

58

59

60

61-62

63

69, 70

NAME

PGND

VOUT

NC

NC(SW)

PVIN

S_OUT

S_IN

M/S

EN_PB

ENABLE

AVIN

POK

AGND

VFB

EAOUT

OCP_ADJ

SS

S_DELAY

MAR1,

MAR2

VSENSE

PGND

FUNCTION

Input/Output power ground. Connect these pins to the ground electrode of the input

and output filter capacitors. See VOUT and PVIN descriptions for more details.

Regulated converter output. Connect to the load, and place output filter capacitor(s)

between these pins and PGND pins 1-4 and 64-68.

NO CONNECT: These pins must be soldered to PCB but not be electrically connected

to each other or to any external signal, voltage, or ground. These pins may be

connected internally. Failure to follow this guideline may result in device damage.

NO CONNECT: These pins are internally connected to the common switching node of

the internal MOSFETs. They must be soldered to PCB but not be electrically

connected to any external signal, ground, or voltage. Failure to follow this guideline

may result in device damage.

Input power supply. Connect to input power supply, place input filter capacitor(s)

between these pins and PGND pins 27-33.

Clock Output. Depending on the mode, either a clock signal or the PWM signal is

output on this pin. These signals are delayed by a time that is related to the resistor

connected between S_DELAY and AGND. Leave this pin floating if not needed.

Clock Input. Depending on the mode, this pin accepts either an input clock to

synchronize the internal switching frequency or the S_OUT signal from another

EN5394QI. Leave this pin floating if it is not used.

This is a Ternary Input. Floating the pin disables parallel operation. A low level

configures the device as Master and a High level configures the device as a slave.

This is the Enable Pre-Bias Input. When this pin is pulled high, the Device will support

monotonic start-up under a pre-biased load. There is a 150kΩ pull-down on this pin.

This is the Device Enable pin. A high level enables the device while a low level

disables the device.

Input power supply for the controller. Needs to be connected to VIN at a quiet point.

Power OK is an open drain transistor for power system state indication. POK is a

logic high when VOUT is with -10% to +20% of VOUT nominal. Being an open drain

output allows several devices to be wired to logically AND the function. Size pull-up

resistor to limit current to 4mA when POK is low.

Ground return for the controller. Needs to be connected to a quiet ground.

External Feedback input. The feedback loop is closed through this pin. A voltage

divider at VOUT is used to set the output voltage. The mid-point of the divider is

connected to VFB. The control loop regulates to make the VFB node voltage 0.6V.

Optional Error Amplifier output. Allows for customization of the control loop.

This pin should be pulled to GND for proper operation of the OCP circuit.

A soft-start capacitor is connected between this pin to AGND. The value of the

capacitor controls the soft-start interval and startup time.

A resistor is connected between this pin and AGND. The value of the resistor controls

the delay in S_OUT. This pin can be left floating if the S_OUT function is not used.

These are 2 ternary input pins. Each pin can be a logical Lo, Logical Hi or Float

condition. 7 of the 9 states are used to modulate the output voltage by 0%, ±2.5%,

±5% or ±10%. The 8th state is used to by-pass the delay in S_OUT. See Functional

Description section.

This pin senses VOUT when the device is placed in the Back-feed (or Pre-bias) mode.

Device thermal pads to be connected to the system gnd plane. See Layout

Recommendations section.

03738

3

October 11, 2013

www.altera.com/enpirion

Rev E