MAX19700 Просмотр технического описания (PDF) - Maxim Integrated

Номер в каталоге

Компоненты Описание

производитель

MAX19700 Datasheet PDF : 32 Pages

| |||

7.5Msps, Ultra-Low-Power

Analog Front-End

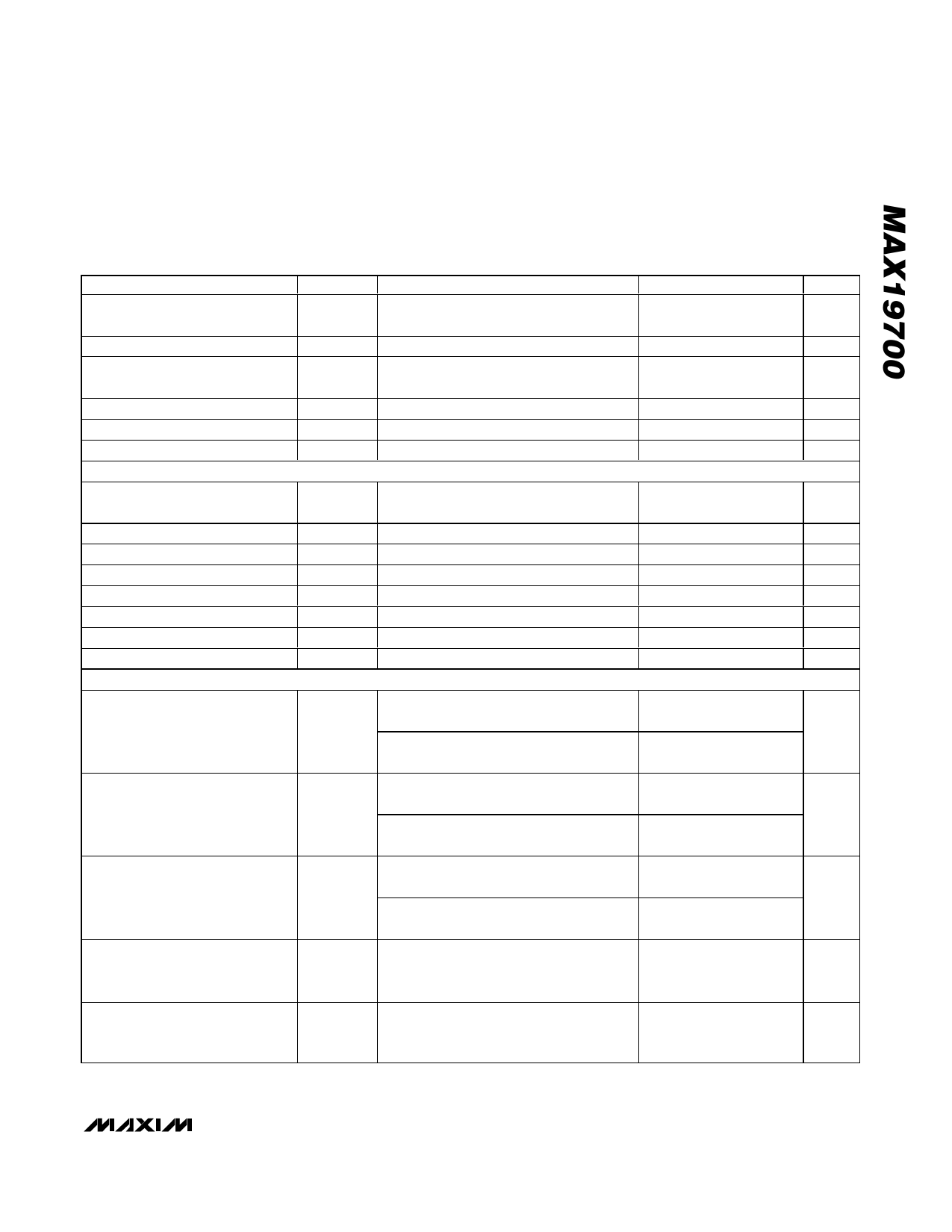

ELECTRICAL CHARACTERISTICS (continued)

(VDD = 3V, OVDD = 1.8V, internal reference (1.024V), CL ≈ 10pF on all digital outputs, fCLK = 7.5MHz (50% duty cycle), ADC input

amplitude = -0.5dBFS, DAC output amplitude = 0dBFS, differential ADC input, differential DAC output, CREFP = CREFN = CCOM =

0.33µF. Typical values are at TA = +25°C, unless otherwise noted. CL < 5pF on all aux-DAC outputs.) (Note 1)

PARAMETER

SYMBOL

CONDITIONS

MIN TYP MAX UNITS

Q-DAC DATA to CLK Rise Setup

Time

CLK Fall to I-DAC Data Hold Time

CLK Rise to Q-DAC Data Hold

Time

tDSQ

tDHI

tDHQ

Figure 5 (Note 6)

Figure 5 (Note 6)

Figure 5 (Note 6)

10

ns

0

ns

0

ns

CLK Duty Cycle

CLK Duty-Cycle Variation

Digital Output Rise/Fall Time

20% to 80%

SERIAL-INTERFACE TIMING CHARACTERISTICS (Figure 6, Note 6)

Falling Edge of CS to Rising Edge

of First SCLK Time

tCSS

DIN to SCLK Setup Time

tDS

DIN to SCLK Hold Time

tDH

SCLK Pulse-Width High

tCH

SCLK Pulse-Width Low

tCL

SCLK Period

SCLK to CS Setup Time

CS High Pulse Width

tCP

tCS

tCSW

MODE-RECOVERY TIMING CHARACTERISTICS (Figure 7)

50

%

±15

%

2.3

ns

10

ns

10

ns

0

ns

25

ns

25

ns

50

ns

10

ns

80

ns

From shutdown to Rx mode, ADC settles

75

to within 1dB SINAD

Shutdown Wake-Up Time

tWAKE,SD

µs

From shutdown to Tx mode, DAC settles to

25

within 10 LSB error

From idle to Rx mode with CLK present

during idle, ADC settles to within 1dB SINAD

7.3

Idle Wake-Up Time (With CLK)

tWAKE,ST0

µs

From idle to Tx mode with CLK present

during idle, DAC settles to 10 LSB error

5

From standby to Rx mode, ADC settles to

within 1dB SINAD

7.3

Standby Wake-Up Time

tWAKE,ST1

µs

From standby to Tx mode, DAC settles to

25

10 LSB error

Enable Time from Tx to Rx, (Ext2-

Tx to Ext2-Rx, Ext4-Tx to Ext4-Rx,

and SPI4-Tx to SPI3-Rx Modes)

tENABLE, RX ADC settles to within 1dB SINAD

500

ns

Enable Time from Rx to Tx, (Ext1-

Rx to Ext1-Tx, Ext4-Rx to Ext4-Tx,

and SPI3-Rx to SPI4-Tx Modes)

tENABLE, TX DAC settles to within 10 LSB error

1

µs

_______________________________________________________________________________________ 7