CY7C1320V18-300BZC Просмотр технического описания (PDF) - Cypress Semiconductor

Номер в каталоге

Компоненты Описание

производитель

CY7C1320V18-300BZC Datasheet PDF : 24 Pages

| |||

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

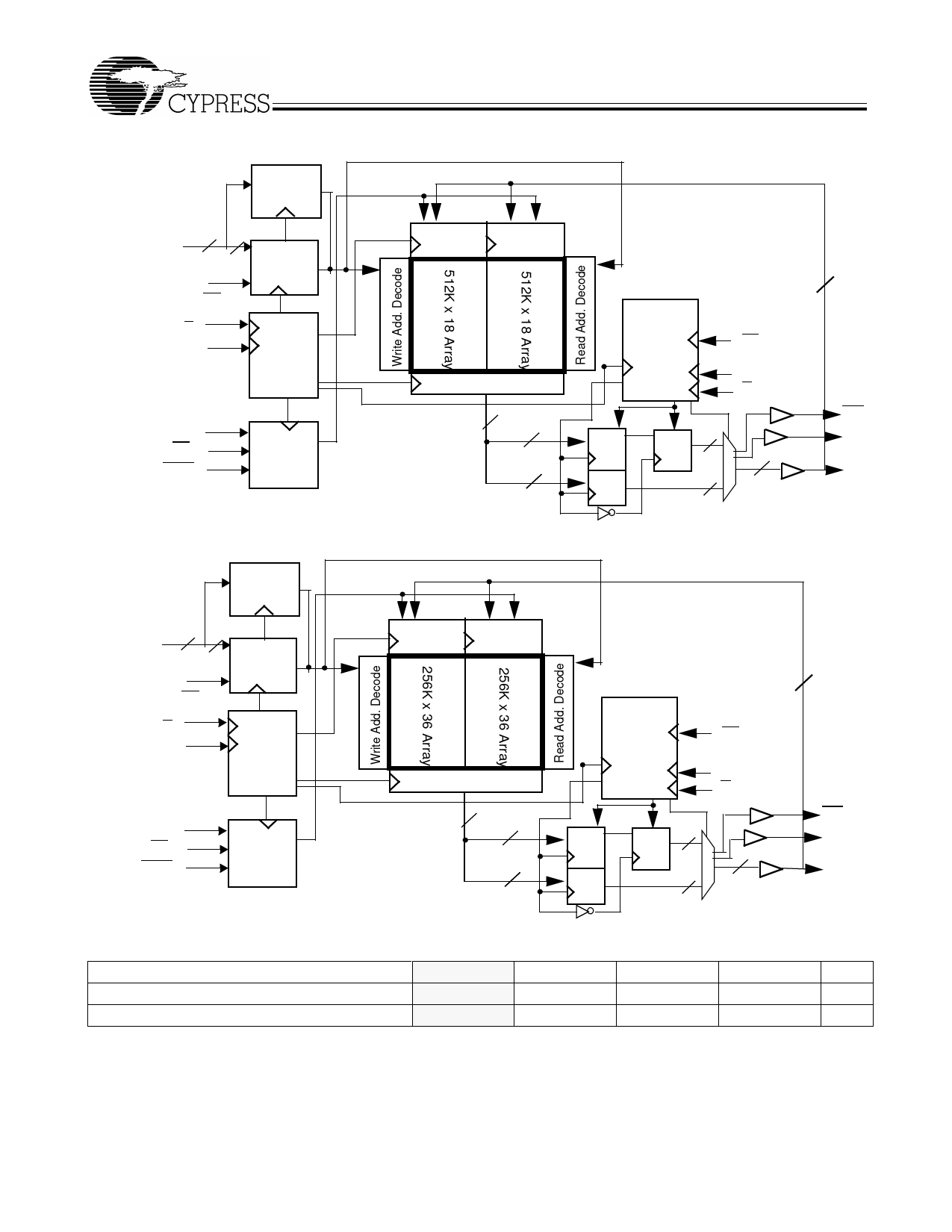

Logic Block Diagram (CY7C1318V18)

A(0)

Burst

Logic

20 19

A(19:0)

Address

A(19:1) Register

LD

K

K

CLK

Gen.

VREF

R/W

BWS[1:0]

Control

Logic

Write

Reg

Write

Reg

Read Data Reg.

36 18

18

Output

Logic

Control

R/W

C

C

Reg.

Reg.

Reg.

18

18

18

CQ

CQ

DQ[17:0]

Logic Block Diagram (CY7C1320V18)

A(0)

Burst

Logic

19 18

A(18:0)

A(18:1)

Address

Register

LD

K

K

CLK

Gen.

Write

Reg

Write

Reg

Read Data Reg.

VREF

R/W

BWS[3:0]

Control

Logic

144 72

72

36

Output

Logic

Control

R/W

C

C

Reg.

Reg. 36

Reg.

36

36

CQ

CQ

DQ[35:0]

Selection Guide[1]

Maximum Operating Frequency

Maximum Operating Current

Note:

1. Shaded cells indicate advanced information.

300 MHz

300

TBD

250 MHz

250

TBD

200 MHz

200

TBD

167 MHz

167

TBD

Unit

MHz

mA

Document #: 38-05177 Rev. *A

Page 2 of 24