X88C64 Просмотр технического описания (PDF) - Xicor -> Intersil

Номер в каталоге

Компоненты Описание

производитель

X88C64 Datasheet PDF : 14 Pages

| |||

X88C64

PRINCIPLES OF OPERATION

The X88C64 is a highly integrated peripheral device for

a wide variety of single-chip microcontrollers. The

X88C64 provides 8K bytes of E2PROM which can be

used either for Program Storage, Data Storage, or a

combination of both in systems based upon Harvard

(80XX) architectures. The X88C64 incorporates the

interface circuitry normally needed to decode the control

signals and demultiplex the Address/Data bus to pro-

vide a “Seamless” interface.

The interface inputs on the X88C64 are configured such

that it is possible to directly connect them to the proper

interface signals of the appropriate single-chip

microcontroller. In the Harvard type system, the reading

of data from the chip is controlled either by the PSEN or

the RD signal, which essentially maps the X88C64 into

both the Program and the Data Memory address map.

The X88C64 is internally organized as two independent

planes of 4K bytes of memory with the A12 input select-

ing which of the two planes of memory are to be

accessed. While the processor is executing code out of

one plane, write operations can take place in the other

plane, allowing the processor to continue execution of

code out of the X88C64 during a byte or page write to the

device.

The X88C64 also features an advanced implementation

of the Software Data Protection scheme, called Block

Protect, which allows the device to be broken into 8

independent sections of 1K bytes. Each of these sec-

tions can be independently enabled for write operations;

thereby allowing certain sections of the device to be

secured so that updates can only occur in a controlled

environment (e.g. in an automotive application, only at

an authorized service center). The desired set-up con-

figuration is stored in a nonvolatile register, ensuring the

configuration data will be maintained after the device is

powered down.

The X88C64 also features a Write Control input (WC),

which serves as an external control over the completion

of a previously initiated page load cycle.

The X88C64 also features the industry standard

E2PROM characteristics such as byte or page mode

write and Toggle Bit Polling.

DEVICE OPERATION

MODES

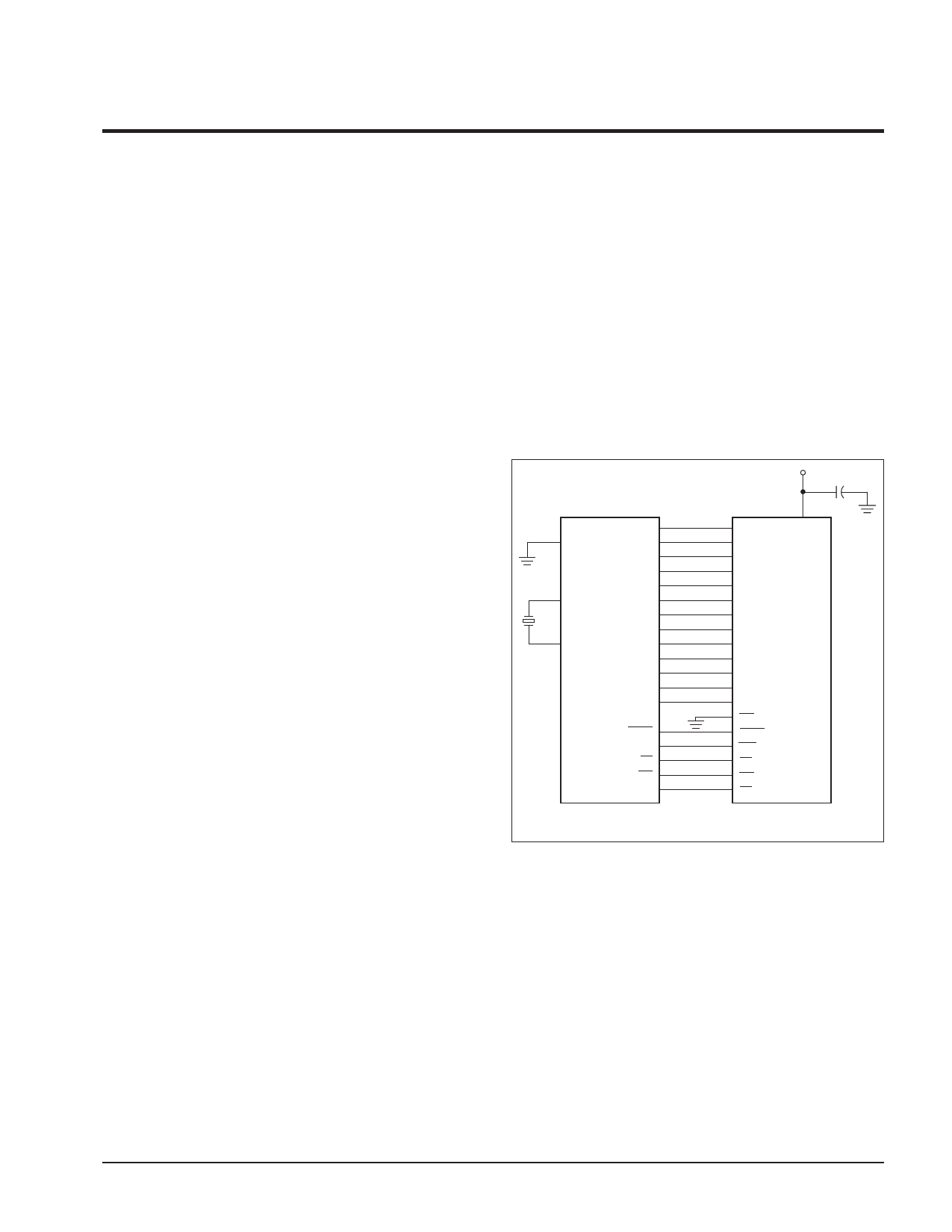

Mixed Program/Data Memory

By properly assigning the address spaces, a single

X88C64 can be used as both the Program and Data

Memory. This would be accomplished by connecting all

of the 8051 control outputs to the corresponding inputs

of the X88C64.

In this configuration, one plane of memory could be

dedicated to Program Storage and the other plane

dedicated to Data Storage. The Data Storage can be

fully protected by enabling block protect write lockout.

TYPICAL APPLICATION

31

EA/VP

19 X1

18

X2

39

P0.0

38

P0.1

37

P0.2

36

P0.3

35

P0.4

34

P0.5

33

P0.6

32

P0.7

21

P2.0

22

P2.1

23

P2.2

24

P2.3

25

P2.4

29

PSEN

30

ALE

17

RD

16

WR

P2.7

80C31

7

8 A/D0

9 A/D1

10 A/D2

11 A/D3

13 A/D4

14 A/D5

15 A/D6

21 A/D7

20 A8

17 A9

19 A10

2 A11

5 A12

6 WC

22 PSEN

18 ALE

23 RD

16 WR

CE

24

VCC

X88C64

3867 FHD F03

Program Memory Mode

This mode of operation is read-only. The PSEN and ALE

inputs of the X88C64 are tied directly to the PSEN and

ALE outputs of the microcontroller. The RD and WR

inputs are tied HIGH.

When ALE is HIGH, the A/D0–A/D7 and A8–A12 ad-

dresses flow into the device. The addresses, both low

and high order, are latched when ALE transitions LOW

(VIL). PSEN will then go LOW and after tPLDV, valid data

is presented on the A/D0–A/D7 pins. CE must be LOW

during the entire operation.

3