SD6830 Просмотр технического описания (PDF) - AUK -> KODENSHI CORP

Номер в каталоге

Компоненты Описание

производитель

SD6830 Datasheet PDF : 34 Pages

| |||

SD6830

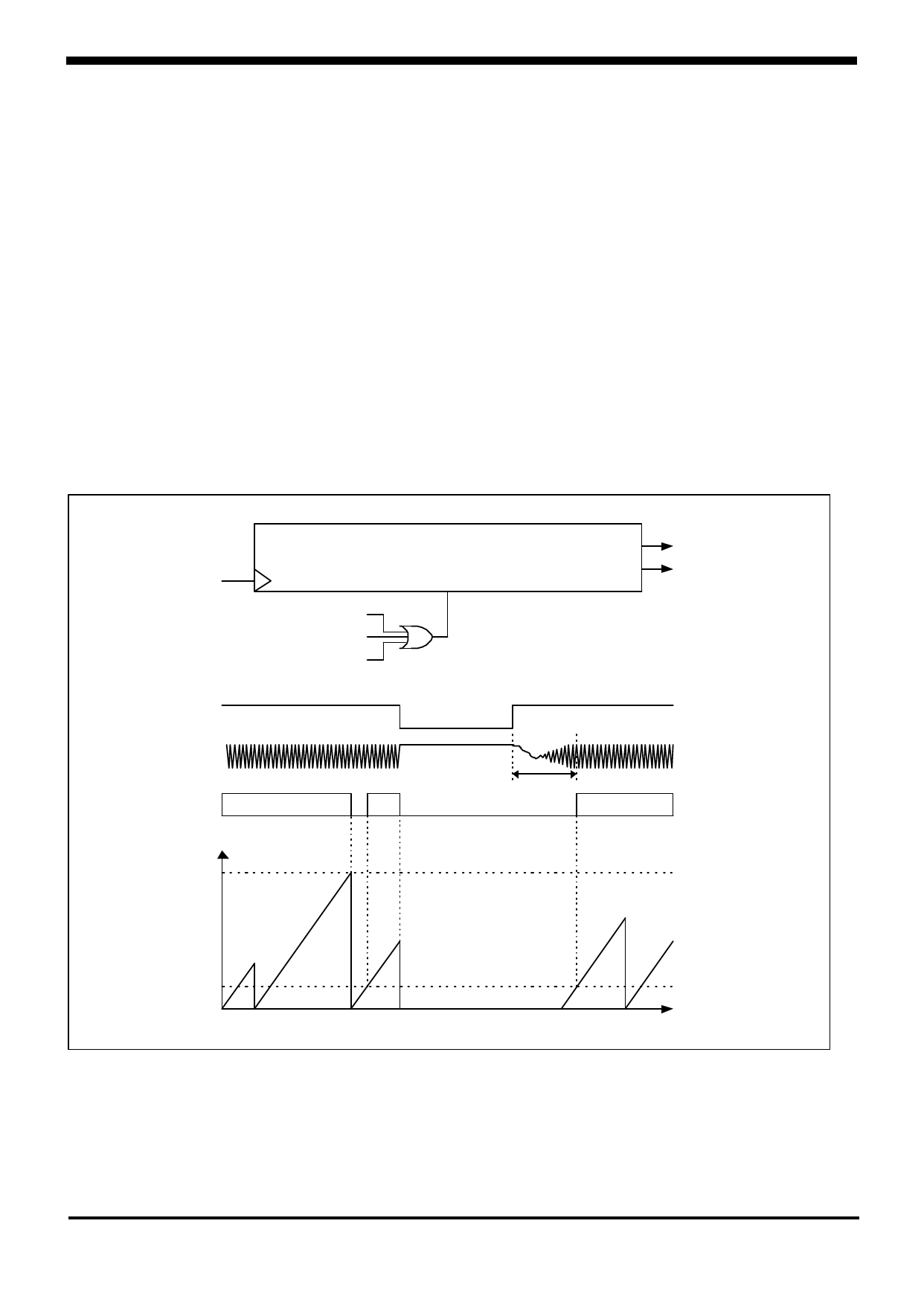

6.11 Watchdog timer (WDT)

The watchdog timer provides the means to return to a reset condition when a system

malfunction occurs and the program enters an infinite loop caused by noise or any

abnormal state.

Also this timer have a function of oscillation stabilization timer. This is a 13-bit counter,

counts the clock which is divided twelve (FSYS/12). In the stop mode the oscillation circuit

stops but when a key input is detected (Port D, Port E) oscillation starts. When 12288 clock

cycles have been counted, the program will be executed from reset address (000H). If the

port C data register’s value does not change from “L” to “H” before the timer counts 98304

clock cycles, a device reset condition is generated.

The oscillator stabilization time : 12/FSYS * 210 = 1/FSYS * 12288 = 27mS (@455KHz)

The time-out period

: 12/FSYS * 213 = 1/FSYS * 98304 = 216mS (@455KHz)

Watchdog Timer (13-bit)

Fsys/12

CLK

Power-on Reset Active

Stop Mode Active

PORT C Data : Low to High Transition

RESET

OPSTART

OVERFLOW

Operating Start

To Reset Logic

OSCOUT

PC

WDT

counting value

98304

Normal

mode

Stop

mode

Watchdog Timer

Overflow

PORT C Data

Low to High

12288

0

STOP

Instruction

Normal

mode

27mS(Min.)

PORT C Data

Low to High

Time

Figure 6-4. Function of Watchdog Timer

KSI-W002-000

12