M80C186EB-8 Просмотр технического описания (PDF) - Intel

Номер в каталоге

Компоненты Описание

производитель

M80C186EB-8 Datasheet PDF : 56 Pages

| |||

M80C186EB

INTRODUCTION

The M80C186EB is the first product in a new gener-

ation of low-power high-integration microproces-

sors It enhances the existing 186 family by offering

new features and new operating modes The

M80C186EB is object code compatible with the

M80C186 M80C188 microprocessors

The feature set of the M80C186EB meets the needs

of low power space critical applications Low-Power

applications benefit from the static design of the

CPU core and the integrated peripherals Minimum

current consumption is achieved by providing a Pow-

erdown mode that halts operation of the device and

freezes the clock circuits Peripheral design en-

hancements ensure that non-initialized peripherals

consume little current

Space critical applications benefit from the inte-

gration of commonly used system peripherals Two

serial channels are provided for services such as

diagnostics inter-processor communication modem

interface terminal display interface and many oth-

ers A flexible chip select unit simplifies memory and

peripheral interfacing The interrupt unit provides

sources for up to 129 external interrupts and will pri-

oritize these interrupts with those generated from

the on-chip peripherals Three general purpose tim-

er counters and sixteen multiplexed I O port pins

round out the feature set of the M80C186EB

OVERVIEW

Figure 1 shows a block diagram of the M80C186EB

The Execution Unit (EU) is an enhanced M8086

CPU core that includes dedicated hardware to

speed up effective address calculations enhance

execution speed for multiple-bit shift and rotate in-

structions and for multiply and divide instructions

string move instructions that operate at full bus

bandwidth ten new instruction and full static opera-

tion The Bus Interface Unit (BIU) is the same as that

found on the original 186 family products except the

queue-status mode has been deleted and buffer in-

terface control has been changed to ease system

design timings An independent internal bus is used

to allow communication between the BIU and inter-

nal peripherals

M80C186EB Core Architecture

REGISTER SET

The M8086 M8088 M80186 M80C186 and

M80C188 all contain the same basic set of registers

instructions and addressing modes The

M80C186EB is upward compatible with all of these

microprocessors

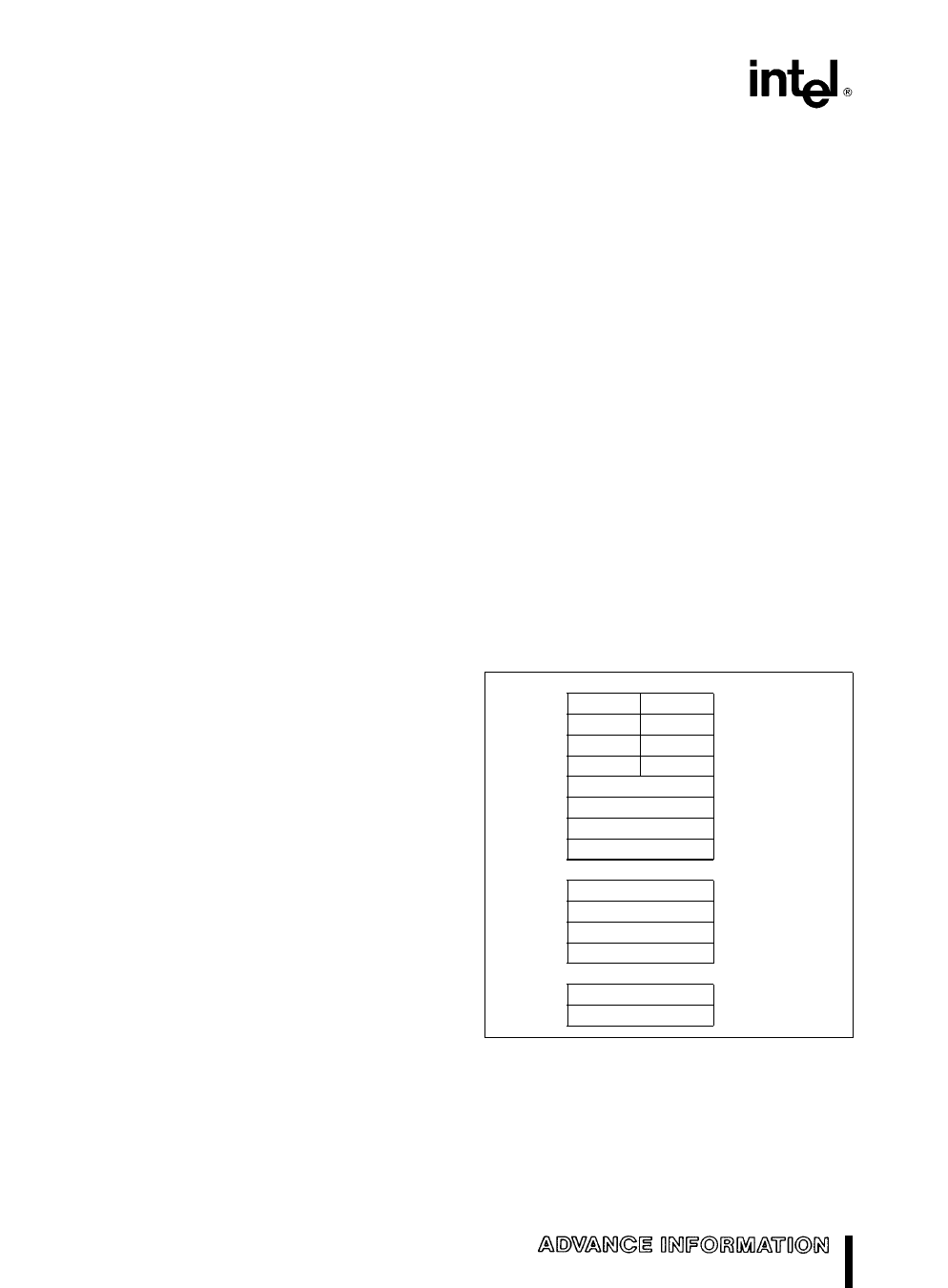

The M80C186EB base architecture has fourteen

16-bit registers as shown in Figure 2 There are eight

general purpose registers which may be used for

arithmetic and logic operands Four of these regis-

ters (AX BX CX and DX) can be used as 16-bit

registers or split into pairs of separate 8-bit registers

The other four registers (BP SI DI and SP) may also

be used to determine offset addresses of operands

in memory These registers may contain base ad-

dresses or indexes to particular locations within a

segment The addressing mode selects the specific

registers for operand and address calculations

Another four 16-bit registers (CS DS ES SS) select

the segments of memory that are immediately ad-

dressable for code stack and data There are two

remaining special purpose registers (IP and F) that

record or alter certain aspects of the M80C186EB

processor state

15

0

AH

AL

AX

BH

BL

BX

CH

CL

CX

DH

DL

DX

Source Index

SI

Destination Index

DI

Base Pointer

BP

Stack Pointer

SP

Code Segment

CS

Stack Segment

SS

Data Segment

DS

Extra Segment

ES

Instruction Pointer

IP

Flags

F

Figure 2 M80C186EB Register Set

4