MAX3881 Просмотр технического описания (PDF) - Maxim Integrated

Номер в каталоге

Компоненты Описание

производитель

MAX3881 Datasheet PDF : 11 Pages

| |||

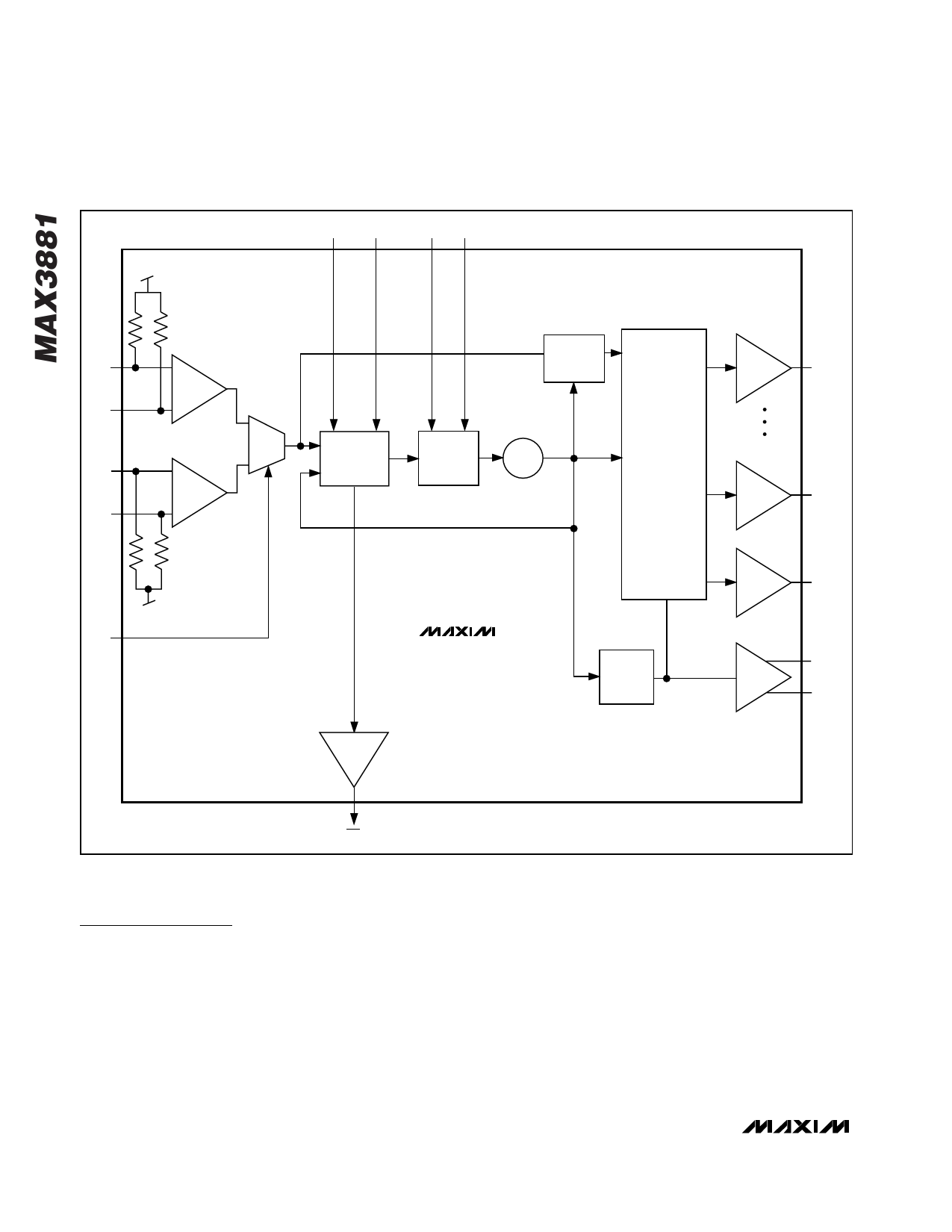

+3.3V, 2.488Gbps, SDH/SONET

1:16 Deserializer with Clock Recovery

PHADJ+ PHADJ-

FIL+ FIL-

VCC

SDI+

SDI-

SLBI+

SLBI-

50Ω

AMP

0

AMP

I

50Ω

0

MUX

I

VCC

SIS

PHASE &

FREQUENCY

DETECTOR

D

Q

CK

PECL

PD15

LOOP

FILTER

VCO

16-BIT

DEMULTIPLEXER

PECL

PD1

MAX3881

CLOCK

DIVIDER

PECL

PD0

PCLK+

PECL

PCLK-

TTL

LOL

Figure 3. MAX3881 Functional Diagram

Detailed Description

The MAX3881 deserializer with clock recovery converts

2.488Gbps serial data to 16-bit-wide, 155Mbps parallel

data. The device combines a fully integrated phase-

locked loop (PLL), input amplifier, data retiming block,

16-bit demultiplexer, clock divider, and PECL output

buffer (Figure 3). The PLL consists of a phase/frequen-

cy detector (PFD), a loop filter, and a voltage-controlled

oscillator (VCO). The MAX3881 is designed to deliver

the best combination of jitter performance and power

dissipation by using a differential signal architecture

and low-noise design techniques. The PLL recovers the

serial clock from the serial input data stream. The

demultiplexer generates a 16-bit-wide 155Mbps paral-

lel data output.

Input Amplifier

The input amplifiers on both the main data and system

loopback accept a differential input amplitude from

50mVp-p to 800mVp-p. The bit error ratio (BER) is bet-

ter than 1 x 10-10 for input signals as small as 9.5mVp-p,

6 _______________________________________________________________________________________