GT28F400B3B150 Просмотр технического описания (PDF) - Intel

Номер в каталоге

Компоненты Описание

производитель

GT28F400B3B150 Datasheet PDF : 49 Pages

| |||

SMART 3 ADVANCED BOOT BLOCK–WORD-WIDE

E

The pin descriptions table details the usage of each device pin.

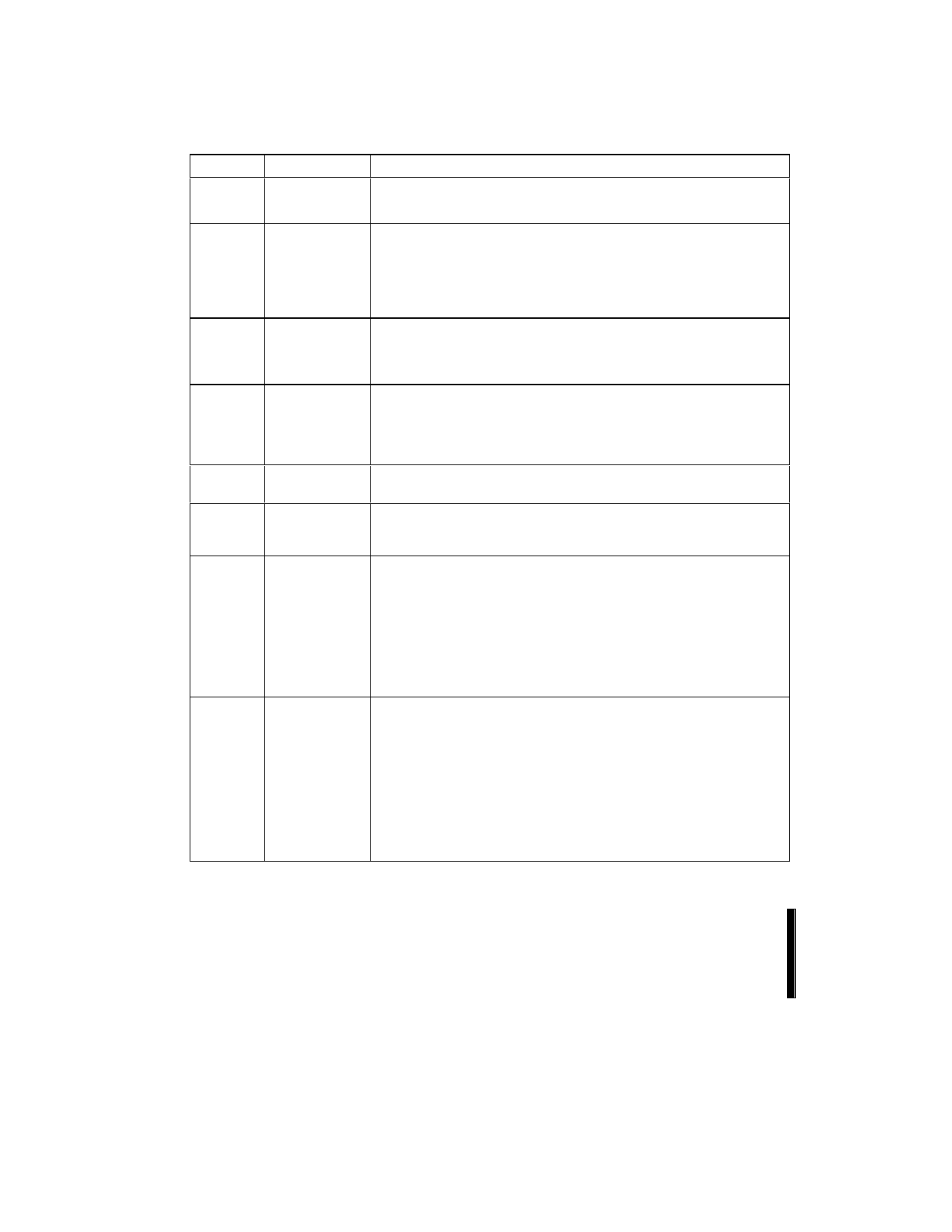

Table 2. 16-Mbit Smart 3 Advanced Boot Block Pin Descriptions

Symbol

A0–A19

DQ0–DQ7

Type

Name and Function

INPUT

ADDRESS INPUTS for memory addresses. Addresses are internally

latched during a program or erase cycle.

28F400B3: A[0-17], 28F800B3: A[0-18], 28F160B3: A[0-19]

INPUT/OUTPUT

DATA INPUTS/OUTPUTS: Inputs array data on the second CE# and

WE# cycle during a Program command. Inputs commands to the

Command User Interface when CE# and WE# are active. Data is

internally latched. Outputs array, Intelligent Identifier and Status Register

data. The data pins float to tri-state when the chip is de-selected or the

outputs are disabled.

DQ8–DQ15

INPUT/OUTPUT

DATA INPUTS/OUTPUTS: Inputs array data on the second CE# and

WE# cycle during a Program command. Data is internally latched.

Outputs array and intelligent identifier data. The data pins float to tri-state

when the chip is de-selected.

CE#

INPUT

CHIP ENABLE: Activates the internal control logic, input buffers,

decoders and sense amplifiers. CE# is active low. CE# high de-selects

the memory device and reduces power consumption to standby levels. If

CE# and RP# are high, but not at a CMOS high level, the standby

current will increase due to current flow through the CE# and RP# inputs.

OE#

INPUT

OUTPUT ENABLE: Enables the device’s outputs through the data

buffers during an array or status register read. OE# is active low.

WE#

INPUT

WRITE ENABLE: Controls writes to the Command Register and memory

array. WE# is active low. Addresses and data are latched on the rising

edge of the second WE# pulse.

RP#

INPUT

RESET/DEEP POWER-DOWN: Uses two voltage levels (VIL, VIH) to

control reset/deep power-down mode.

When RP# is at logic low, the device is in reset/deep power-down

mode, which drives the outputs to High-Z, resets the Write State

Machine, and draws minimum current.

When RP# is at logic high, the device is in standard operation.

When RP# transitions from logic-low to logic-high, the device defaults to

the read array mode.

WP#

INPUT

WRITE PROTECT: Provides a method for locking and unlocking the two

lockable parameter blocks.

When WP# is at logic low, the lockable blocks are locked,

preventing program and erase operations to those blocks. If a program

or erase operation is attempted on a locked block, SR.1 and either SR.4

[program] or SR.5 [erase] will be set to indicate the operation failed.

When WP# is at logic high, the lockable blocks are unlocked and

can be programmed or erased.

See Section 3.3 for details on write protection.

10

PRELIMINARY