CDP1821C Просмотр технического описания (PDF) - Intersil

Номер в каталоге

Компоненты Описание

производитель

CDP1821C Datasheet PDF : 7 Pages

| |||

CDP1821C/3

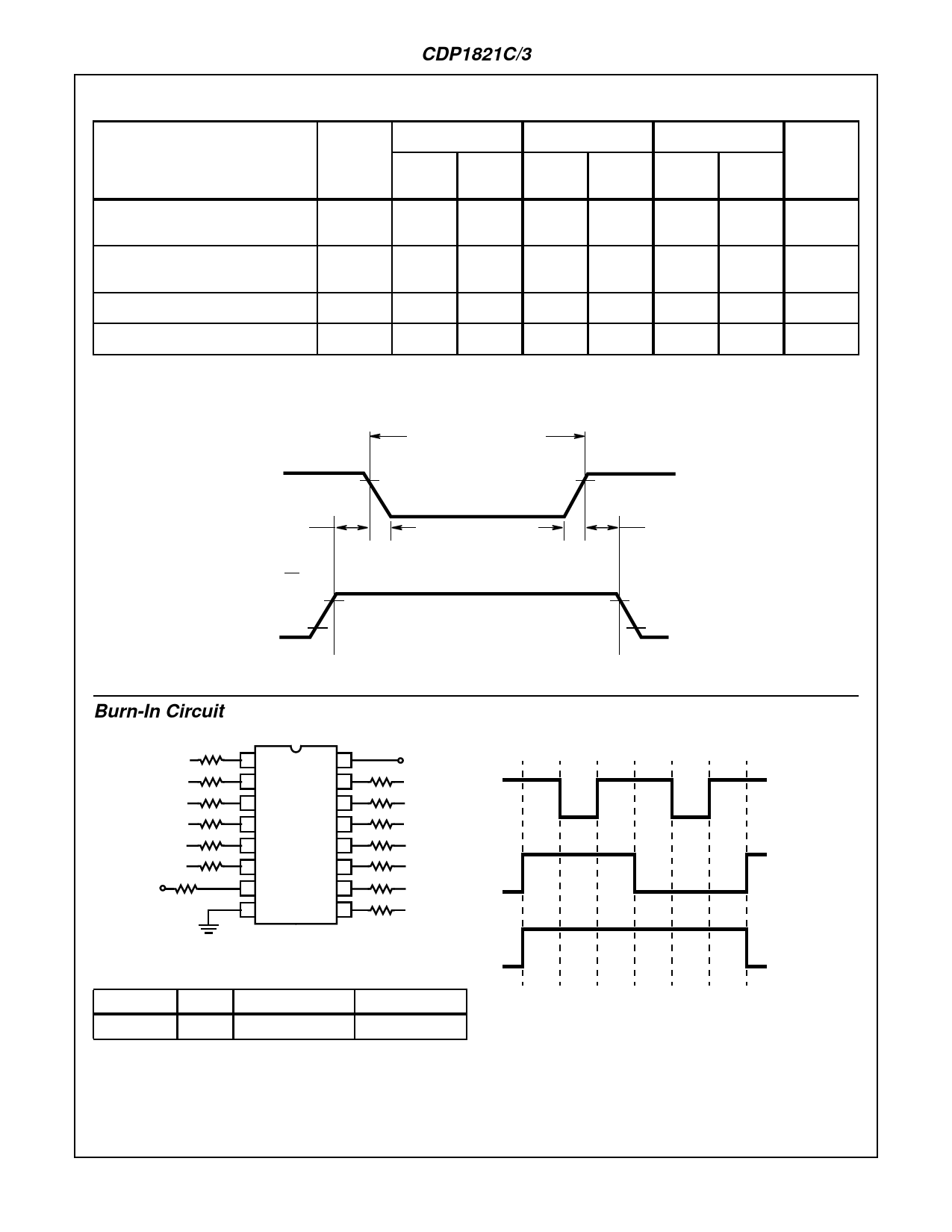

Data Retention Specifications

TEST CONDITIONS

-55oC, +25oC

+125oC

PARAMETER

VDR

VDD

SYMBOL

(V)

(V)

MIN

MAX

MIN

MAX

Minimum Data Retention Voltage

VDD

-

-

-

2

-

2.5

(Note 1)

Data Retention Quiescent Current

IDD

2

-

-

50

-

200

(Note 1)

Chip Deselect to Data Retention Time

tCDR

-

5

450

-

650

-

Recovery to Normal Operation Time

tRC

-

5

450

-

650

-

NOTE:

1. 100% testing. All other limits are designer’s parameters under given test conditions and do not represent 100% testing

UNITS

V

µA

ns

ns

DATA RETENTION MODE

VDD

0.95 VDD

0.95 VDD

VDR

tCDR

tF

tR

tRC

CS

VIH

VIL

VIH

VIL

Burn-In Circuit

FIGURE 3. LOW VDD DATA RETENTION WAVEFORMS AND TIMING DIAGRAM

R

A11

1

R

A0

2

R

A1

3

R

A2

4

R

A3

5

R

A4

6

VDD/2

7

RI

8

16

R

VDD

15

A10

R

14

O1

R

13

A9

R

12

A8

R

11

A7

R

10

A6

R

9

A5

R = 8.2kΩ 20%

RI = 2kΩ 20%

PACKAGE

D

VDD

7V

TEMPERATURE

+125oC

DURATION

160 Hrs.

0

O1

1.6 2.2 5.0 6.6 7.2 10.0 µs

VDD

0

VDD

A0

0

VDD

A1

0

A1 - A11 ARE DIVISION BY 2 BASED ON A0

FIGURE 4. DYNAMIC/OPERATING BURN-IN CIRCUIT AND TIMING DIAGRAM

6-10