78P7200L Просмотр технического описания (PDF) - TDK Corporation

Номер в каталоге

Компоненты Описание

производитель

78P7200L Datasheet PDF : 24 Pages

| |||

78P7200L

E3/DS3/STS-1

Transceiver

FUNCTIONAL DESCRIPTION

The 78P7200L is a single chip line interface IC

designed to work with a 51.84 Mbit/s STS-1, 44.736

Mbit/s DS3 or 34.368 Mbit/s E3 signal. The receiver

recovers clock, positive data and negative data from

an Alternate Mark Inversion (AMI) signal. The AMI

line input signal should be B3ZS or HDB3 coded.

The transmitter accepts clock, positive, and negative

data and converts them into an AMI signal to drive a

75Ω coaxial cable. The shape of the transmitted

signal though any cable length of 0 to 450 feet complies

with the published templates of ANSI T1.102-1993,

Telcordia TR-NWT-000499 and GR-253-CORE, ITU-T

G.703. The 78P7200L is designed to work with B3ZS

or HDB3 coded signals. The B3ZS or HDB3 encoding

and decoding functions can be included in the framer

ICs. The 78P7200L is designed to easily connect to

popular ATM framer ICs such as PMC 7345 (SUNI-

PDH), PMC 7346 (QJET) and 7321.

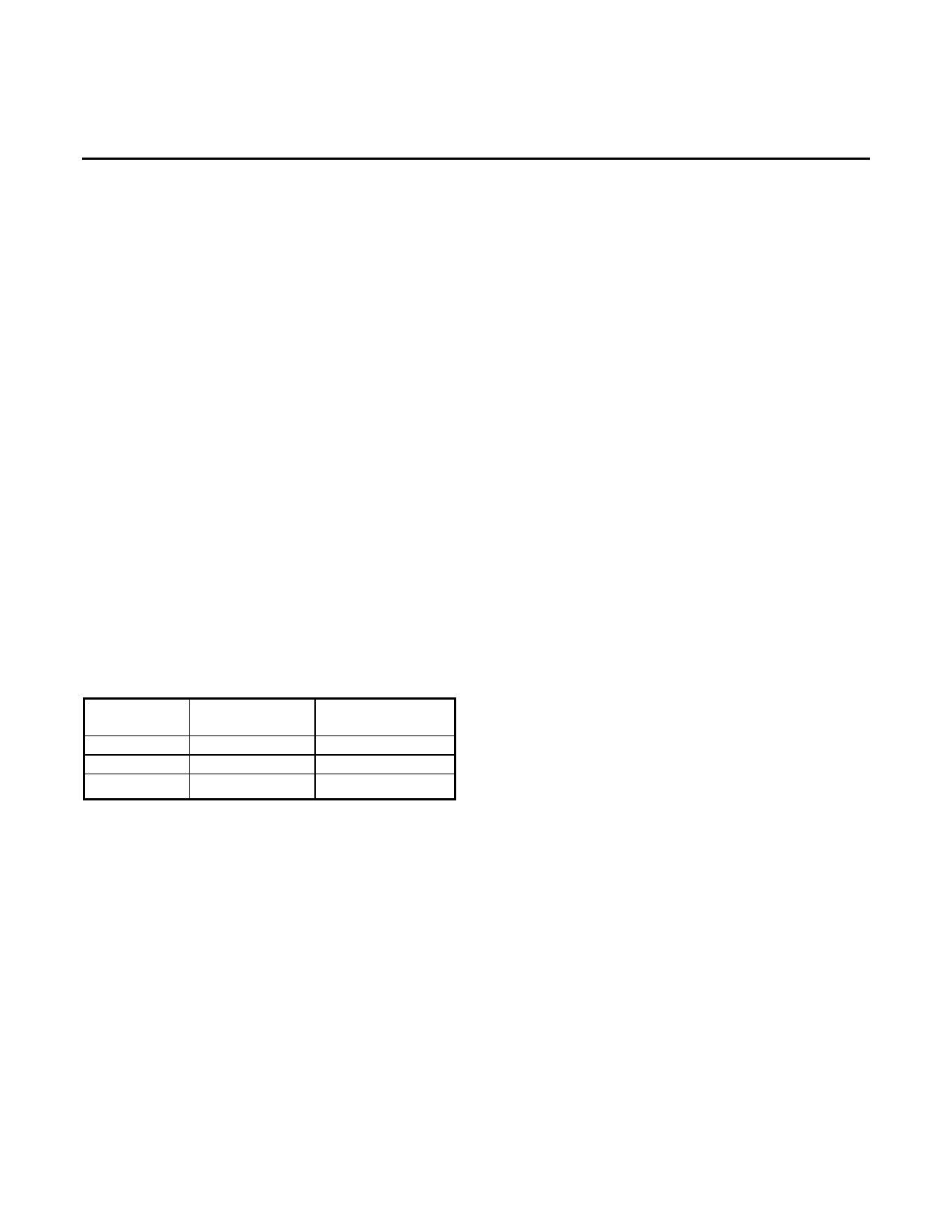

OPERATION SPEED

Internal bias generators that are adjusted by the value of

the RFO set the 78P7200L PLL center frequency and

Transmitter amplitude for the different standards. The E#

pin controls the equalizer response and the transmitter

pulse shape and amplitude. The following table shows

the proper settings.

STANDARD

E3

DS3

STS-1

RFO VALUE,

KΩ

6.81

5.23

4.53

E# PIN SETTING

Low

High

Float

RECEIVER

The receiver input can be either transformer-coupled

or capacitor coupled to the AMI signal. In

applications where the highest performance and

isolation is required, a 1:1 transformer is used on the

receiver path. In the applications, where isolation is

provided elsewhere in the circuit, an AC coupling

can be used. The inputs to the IC are internally

referenced to Vcc. Since the input impedance of the

78P7200L is high, the AMI line must be terminated

to 75Ω. The input signal of the 78P7200L must be

limited to a maximum of three consecutive zeros

using a coding scheme such as B3ZS or HDB3.

The AMI signal first enters an equalizer and AGC

gain stage. The equalizer is designed to overcome

intersymbol interference caused by long cables.

Because the equalizer is adaptive, the circuit will work

with all square shaped signals such as DS3 high or 34

Mbit/s E3. The variable gain differential amplifier

maintains a constant voltage level output regardless

of the input voltage level. The gain of the amplifier is

adjusted by detecting the peak of the signal and

comparing it to a fixed reference.

Outputs of the data comparators are connected to

the clock recovery circuits. The clock recovery

system employs a phase locked loop with an

auxiliary frequency-sensitive acquisition loop. This

system permits the loop to independently lock to the

frequency and phase of the incoming data stream

without the need for an external, high precision

tuned circuits or reference clock signal.

The jitter tolerance of the 78P7200L meets the

requirements of Telcordia GR-499-CORE for

Category I equipment for DS3 rates and exceeds the

requirements of ITU-T G.823 for E3 rates.

2