KE5BGCA256A Просмотр технического описания (PDF) - KAWASAKI MICROELECTRONICS

Номер в каталоге

Компоненты Описание

производитель

KE5BGCA256A Datasheet PDF : 114 Pages

| |||

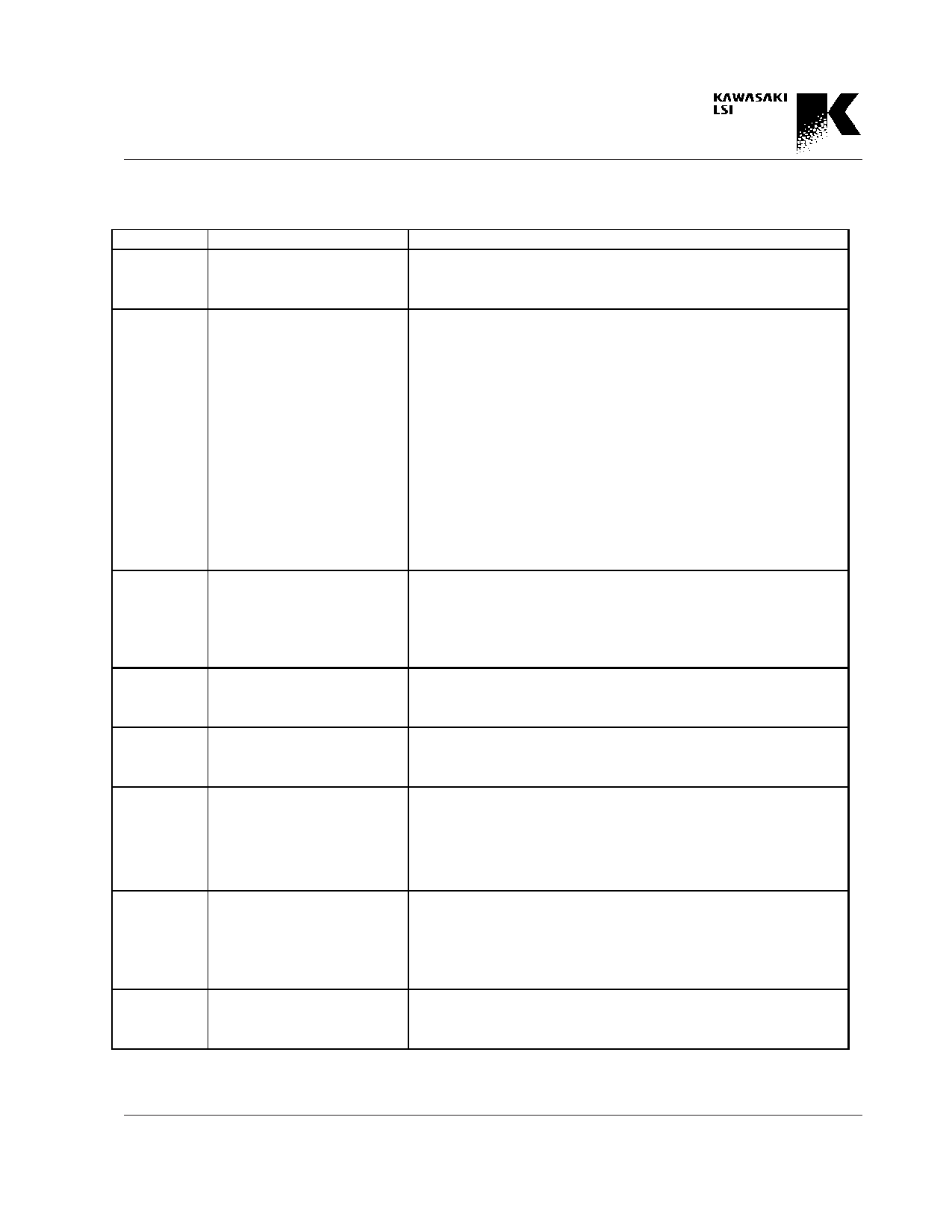

3.2 Pin Descriptions

Pin name

CLK

Attribute

CLOCK

Inp ut

LVTTL

PHASE

PHASE

Inp ut

LVTTL

GigabitCAM KE5BGCA256

Function

CLK is the master clock input. Other input signals are referred to the

rising edge of CLK.

PHASE determines the action timing of the device. The latency of the

output is also determined by the relationship between PHASE and

CLK.

Regardless of whether the input mode is 32 bits (Normal Access

Mode) or 64 bits (First Access Mode), two cycles of the CLK signals

are necessary. PHASE regulates the input timing of the data input

from 32-bit DAT<31:0> when the input mode is 64 bits .

W hen PHASE is high, the data on DAT<31:0> is input in the 32 bits

on the MSB side of 64 bits. W hen PHASE is low,

the data is input in the 32 bits on the LSB side. When the input mode

is 32 bits, the 32-bit data is written in the register designated by

ADD<5:0> on the rising edge of CLK while PHASE is low.

DAT<3 1:0 >

ADD<5:0 >

CEN

RWN

OEDATN

SRCHN

CPU Bus

Inp ut/Outp ut

Tristate LVTTL

CPU Bus Address Bus

Inp ut

LVTTL

Device Enable

Inp ut

LVTTL

Read/Write

Inp ut

LVTTL

CPU Bus Output Enable

Inp ut

LVTTL

Search Enable

Inp ut

LVTTL

DATA<31:0> is a 32-bit, bidirectional data bus used to convey data,

to execute commands, and to write/read to and from the registers. The

direction is controlled by RWN and there is latency when the bus is

s witched .

ADD<5:0> is a 6-bit address bus used to select registers.

CEN is used to access the CPU port. The active CEN enables the

input operation of data and command.

RWN is used to determine the direction of the CPU bus. RWN low

selects a write cycle, and RW N high selects a read cycle. There is

latency between the RWN change and the output as the result of the

data bus change.

OEDATN controls the CPU bus output. OEDATN low enables the

output of the CPU bus by the read operation, and OEDATN high

makes the CPU bus have high impedance despite the output

indication by the read operation. There is latency between the

OEDATN change and its result.

SRCHN enables the search operation together with the write

operation to the comparand register.

Preliminary

3-4