HFA3841 Просмотр технического описания (PDF) - Intersil

Номер в каталоге

Компоненты Описание

производитель

HFA3841 Datasheet PDF : 27 Pages

| |||

Preliminary - HFA3841

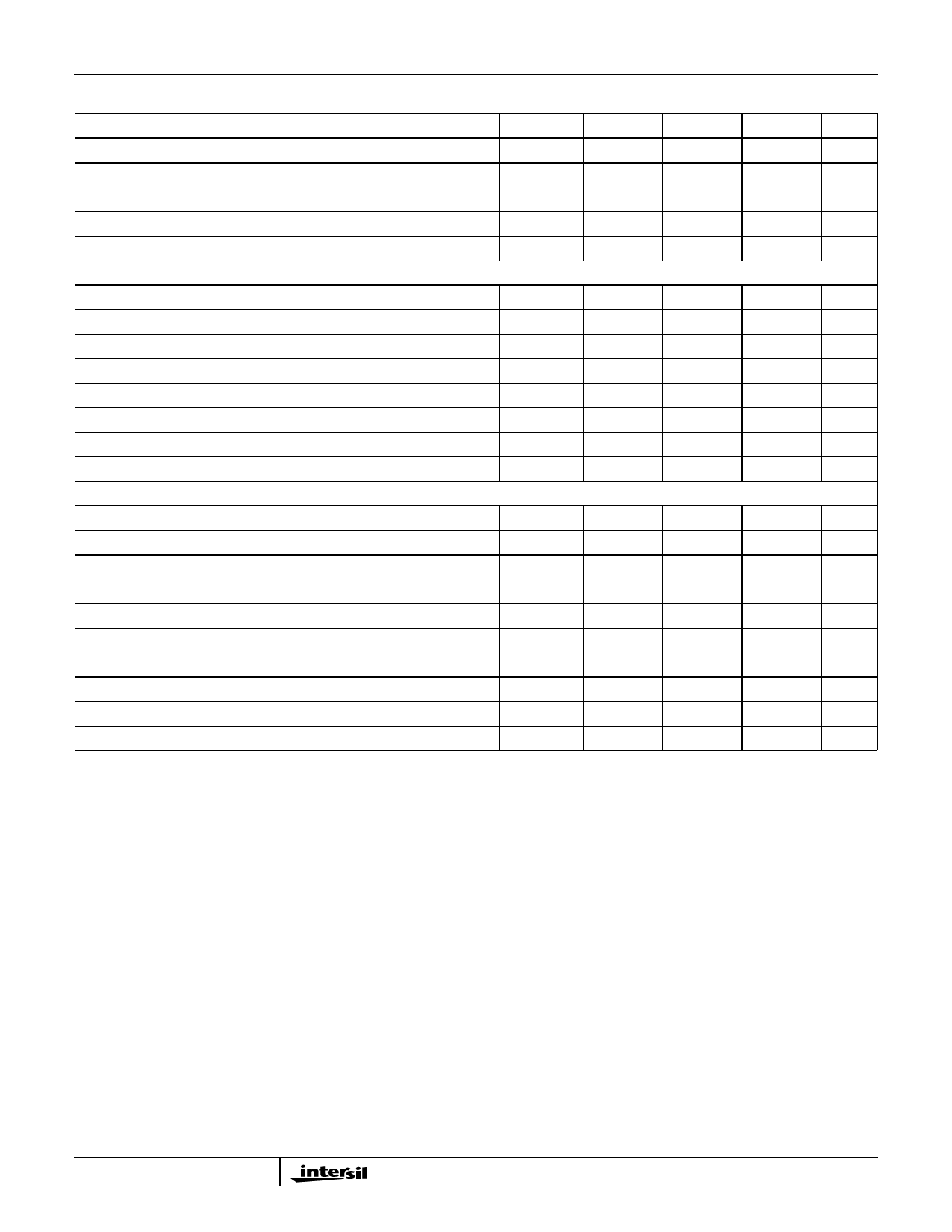

AC Electrical Specifications (Continued)

PARAMETER

SYMBOL

MIN

TYP

MAX

UNITS

SIOIS16N Delay Falling from Address

SIOIS16N Delay Rising from Address

SWAITN Delay Falling from IOWRN

SWAITN Width Time

SIOWRN High from SWAITN High

RADIO TX DATA - TX PATH

tDFIOIS16

-

tDRIOIS16

-

tDFWT

-

tWWT

-

tDRIOWR

0

-

35

ns

-

35

ns

-

35

ns

-

12,000

ns

-

-

ns

TXC Rising to TXD

TXC Period

TXC Width Hi

TXC Width Lo

MCLK Period

TXC Rising to TX_PE2 Deassert (See Note 9)

TX_RDY Assert Before TXC Rising

TX_RDY Hold After TXC Rising (See Note 2)

RADIO RX DATA - RX PATH

tDTXD

tTXC

tCHM

tCLM

ttMCK

tDTX_PE2

tTX_RDY

tTX_RDYH

-

4* tTMCK

31

31

22.7

-

10

0

-

-

-

-

-

TBD

-

-

10

ns

-

ns

-

ns

-

ns

-

ns

TBD

ns

-

ns

-

RX_RDY Setup Time to RXC Positive Edge (See Note 3)

tSURX_RDY

10

-

-

ns

RX_RDY Hold Time from RXC Positive Edge (See Note 4)

tHRX_RDY

45

-

-

ns

RX_PE2 Delay from RX_RDY deAssert (See Note 8)

tDRX_PE2

-

3 * tMCLK

-

ns

RX_PE2 Low Pulse Width (See Note 7)

tWRX_PE2

-

4 * tMCLK

-

ns

RXD Setup Time to RXC Positive Edge (See Note 5)

tSURXD

10

-

-

ns

RXD Hold Time from RXC Positive Edge (See Note 5)

tHRXD

0

-

-

ns

RXC Period (See Note 9)

tRXC

-

3 * tMCLK

-

ns

MCLK Period

tMCLK

22.7

-

-

ns

RXC Width Hi

tRCHM

31

-

-

ns

RXC Width Lo

tRCLM

31

-

-

ns

NOTES:

2. TX_RDY is and'd with TXC_ONE_SHOT to shift data in shift register. However, once the last data bit is put on TXD output pin no further shifting

of bits is required. In addition, TX_RDY remains asserted until TX_PE2 is de-asserted which occurs several MAC MCLK's after the last data bit

is shifted into the BBP TX_PORT. Therefore, 0ns hold time is required for this signal.

TX_RDY is used by the BBP to signal that the PLCP header and preamble have been generated and the MAC must provide the MPDU data.

TX_RDY will remain asserted until TX_PE2 is deasserted by the MAC.

TX_PE2 is async to the TX_PORT.

3. MD_RDY is and'd with RXC_ONE_SHOT (RXDAV) to shift data in shift register. RX_RDY is not required to be valid until 1 MCLK after RXC is

sampled high. Therefore, a negative setup time could be used. Since this is an unlikely scenario, we will leave it at a nominal 10ns setup time.

4. MD_RDY is and'd with RXC_ONE_SHOT (RXDAV) to shift data in shift register. Therefore, for the last data bit, the MD_RDY must be held active

until RXC_ONE_SHOT is sampled high by MAC's MCLK. However, it is assumed that BBP will be used in a mode that keeps RX_RDY

(MD_RDY) and RXC running until RX_PE2 is de-asserted. The MAC will stop processing data after the number of bits retrieved from the PLCP

header length field are received. THEREFORE, the RX_RDY hold time with respect to RXC does not matter. However, should the RX_RDY

signal be cleared when the last RXD bit is received the hold time w/r RXC must be honored.

5. RXC positive edge clocks a flop which stores the RXD for internal usage.

6. RXC period (and Hi/Lo times) must be long enough for flops clocked by MAC MCLK to see 1 RXC high and 1 RXC low. Since RXC can be async

to MAC MCLK it is assumed that 3 MCLK periods will suffice.

7. RX_PE inactive width at BBP is 3 BBP MCLK's. Since BBP MCLK and MAC MCLK can be async minimum should be 4 MAC MCLK's.

8. Not yet verified, but seems reasonable. When RX_RDY drops before expected number of RXD bits is received, then Tx/Rx FSM in mpctl.v

signals timers which clear rx_pe2_int. More of a functional spec than a timing spec.

9. Need to sample 1 RXC high and 1 RXC low with MAC MCLK.

9