ICL8068/ICL7104 Просмотр технического описания (PDF) - Intersil

Номер в каталоге

Компоненты Описание

производитель

ICL8068/ICL7104 Datasheet PDF : 21 Pages

| |||

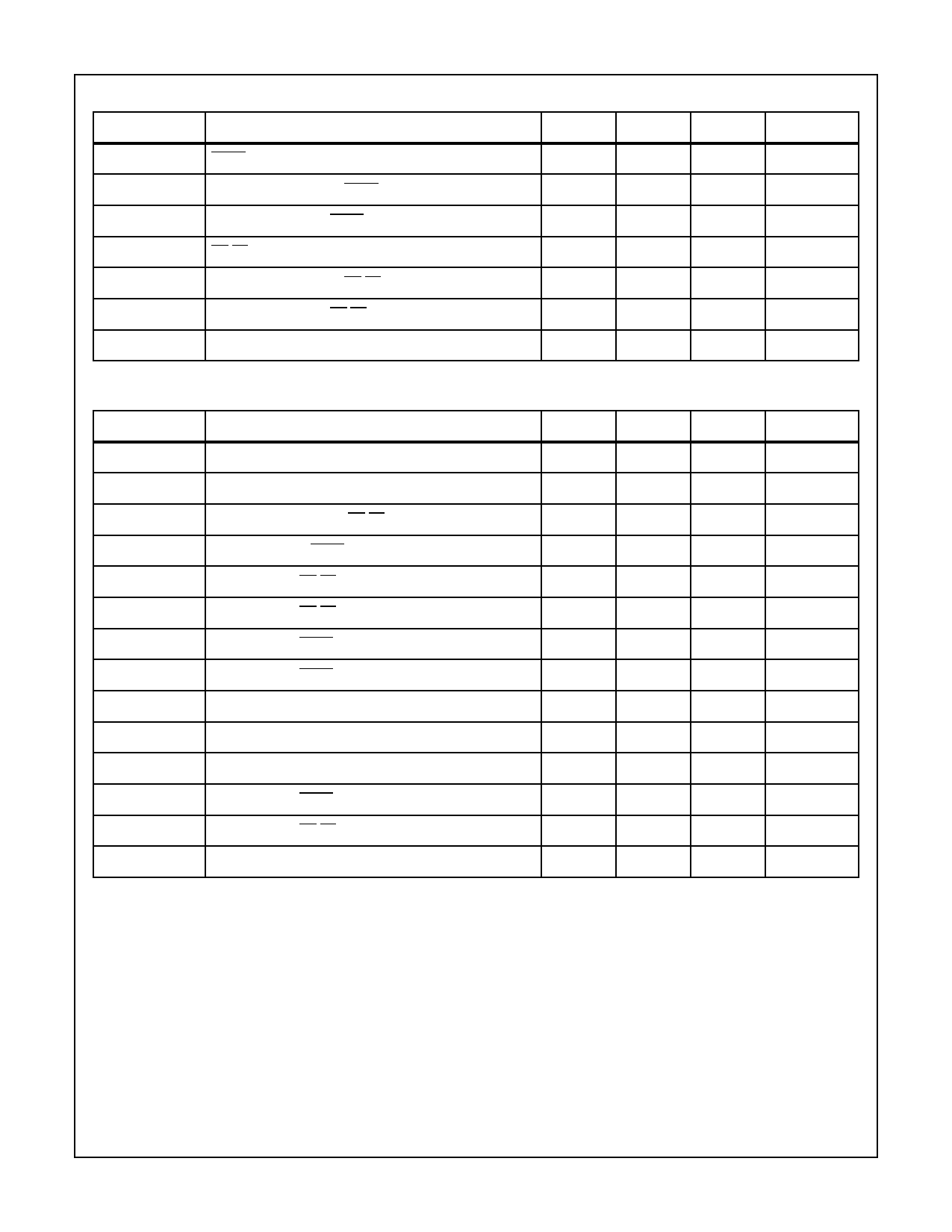

SYMBOL

tBEA

tDAB

tDHB

tCEA

tDAC

tDHC

tCWH

ICL8052/ICL7104, ICL8068/ICL7104

TABLE 1. DIRECT MODE TIMING REQUIREMENTS (Note: Not tested in production)

DESCRIPTION

MIN

TYP

MAX

XBEN (Min) Pulse Width.

-

300

-

Data Access Time from XBEN.

-

300

-

Data Hold Time from XBEN.

-

200

-

CE/LD Min. Pulse Width.

-

350

-

Data Access Time from CE/LD.

-

350

-

Data Hold Time from CE/LD.

-

280

-

CLOCK 1 High Time.

-

1000

-

SYMBOL

tMW

tSM

tME

tMB

tCEL

tCEH

tCBL

tCBH

tCDH

tCDL

tSS

tCBZ

tCEZ

tCWH

TABLE 2. HANDSHAKE TIMING REQUIREMENTS (Note: Not tested in production)

DESCRIPTION

MIN

TYP

MAX

Mode Pulse (Min).

-

20

-

Mode Pin Set-Up Time.

-

-150

-

Mode Pin High to Low Z CE/LD High Delay.

-

200

-

Mode Pin High to XBEN Low Z (High) Delay.

-

200

-

Clock 1 High to CE/LD Low Delay.

-

700

-

Clock 1 High to CE/LD High Delay.

-

600

-

Clock 1 High to XBEN Low Delay.

-

900

-

Clock 1 High to XBEN High Delay.

-

700

-

Clock 1 High to Data Enabled Delay.

-

1100

-

Clock 1 Low to Data Disabled Delay.

-

1100

-

Send ENABLE Set-Up Time.

-

-350

-

Clock 1 High to XBEN Disabled Delay.

-

2000

-

Clock 1 High to CE/LD Disabled Delay.

-

2000

-

Clock 1 High Time.

1250

1000

-

UNIT

ns

ns

ns

ns

ns

ns

ns

UNIT

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

5-15