LTC1419C Просмотр технического описания (PDF) - Linear Technology

Номер в каталоге

Компоненты Описание

производитель

LTC1419C Datasheet PDF : 20 Pages

| |||

LTC1419

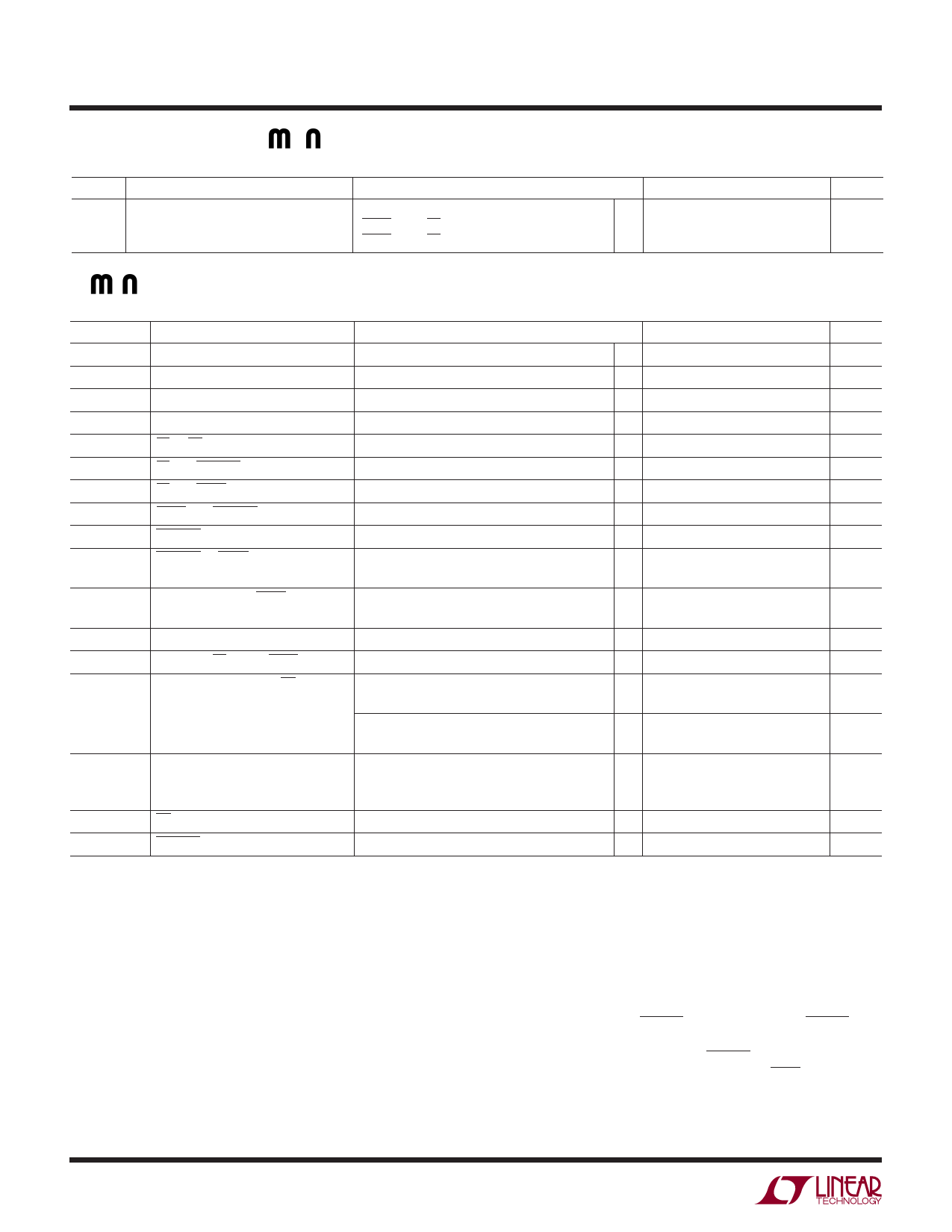

POWER REQUIRE E TS The ● denotes specifications which apply over the full operating temperature range,

otherwise specifications are at TA = 25°C. (Note 5)

SYMBOL PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

PDIS

Power Dissipation

Nap Mode

SHDN = 0V, CS = 0V

●

150

240

mW

7.5

12

mW

Sleep Mode

SHDN = 0V, CS = 5V

1.2

mW

WU

TI I G CHARACTERISTICS The ● denotes specifications which apply over the full operating temperature

range, otherwise specifications are at TA = 25°C. (Note 5)

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

fSAMPLE(MAX) Maximum Sampling Frequency

● 800

kHz

tCONV

Conversion Time

●

950

1150

ns

tACQ

Acquisition Time

●

90

300

ns

tACQ + CONV

t1

Acquisition + Conversion Time

CS to RD Setup Time

(Notes 9, 10)

●

1040

1250

ns

●0

ns

t2

CS↓ to CONVST↓ Setup Time

(Notes 9, 10)

● 40

ns

t3

CS↓ to SHDN↓ Setup Time

(Notes 9, 10)

t4

SHDN↑ to CONVST↓ Wake-Up Time (Note 10)

40

ns

400

ns

t5

CONVST Low Time

(Notes 10, 11)

● 40

ns

t6

CONVST to BUSY Delay

CL = 25pF

20

ns

●

50

ns

t7

Data Ready Before BUSY↑

20

50

ns

● 15

ns

t8

Delay Between Conversions

(Note 10)

● 40

ns

t9

Wait Time RD↓ After BUSY↑

(Note 9)

● –5

ns

t10

Data Access Time After RD↓

CL = 25pF

15

25

ns

●

35

ns

CL = 100pF

20

35

ns

●

50

ns

t11

Bus Relinquish Time

0°C ≤ TA ≤ 70°C

– 40°C ≤ TA ≤ 85°C

10

20

ns

●

25

ns

●

30

ns

t12

RD Low Time

● t10

ns

t13

CONVST High Time

● 40

ns

Note 1: Stresses beyond those listed under Absolute Maximum Ratings

may cause permanent damage to the device. Exposure to any Absolute

Maximum Rating condition for extended periods may affect device

reliabilty and lifetime.

Note 2: All voltage values are with respect to ground with DGND and

AGND wired together unless otherwise noted.

Note 3: When these pin voltages are taken below VSS or above VDD, they

will be clamped by internal diodes. This product can handle input currents

greater than 100mA below VSS or above VDD without latchup.

Note 4: When these pin voltages are taken below VSS, they will be clamped

by internal diodes. This product can handle input currents greater than

100mA below VSS without latchup. These pins are not clamped

to VDD.

Note 5: VDD = 5V, VSS = – 5V, fSAMPLE = 800kHz, tr = tf = 5ns unless

otherwise specified.

Note 6: Linearity, offset and full-scale specifications apply for a single-

ended +AIN input with – AIN grounded.

Note 7: Integral nonlinearity is defined as the deviation of a code from a

straight line passing through the actual endpoints of the transfer curve.

The deviation is measured from the center of the quantization band.

Note 8: Bipolar offset is the offset voltage measured from – 0.5LSB

when the output code flickers between 0000 0000 0000 00 and

1111 1111 1111 11.

Note 9: Guaranteed by design, not subject to test.

Note 10: Recommended operating conditions.

Note 11: The falling edge of CONVST starts a conversion. If CONVST

returns high at a critical point during the conversion it can create small

errors. For best performance ensure that CONVST returns high either

within 650ns after the start of the conversion or after BUSY rises.

1419fb

4