DS2188 Просмотр технического описания (PDF) - Dallas Semiconductor -> Maxim Integrated

Номер в каталоге

Компоненты Описание

производитель

DS2188 Datasheet PDF : 10 Pages

| |||

DS2188

T1/CEPT Jitter Attenuator

www.dalsemi.com

FEATURES

Attenuates clock and data jitter present in T1

or CEPT lines

Meets the jitter attenuation templates

outlined in TR62411, TR-TSY-000170,

G.735, and G.742

Only one external component required; either

a 6.176 MHz (T1) or 8.192 MHz (CEPT)

crystal

Selectable buffer size of 128 or 32 bits

Jitter attenuation is easily disabled

Single +5V supply; low-power CMOS

technology

Available in 16-pin DIP and 16-pin SOIC

(DS2188S)

Companion to the DS2186 Transmit Line

and DS2187 Receive Line Interface

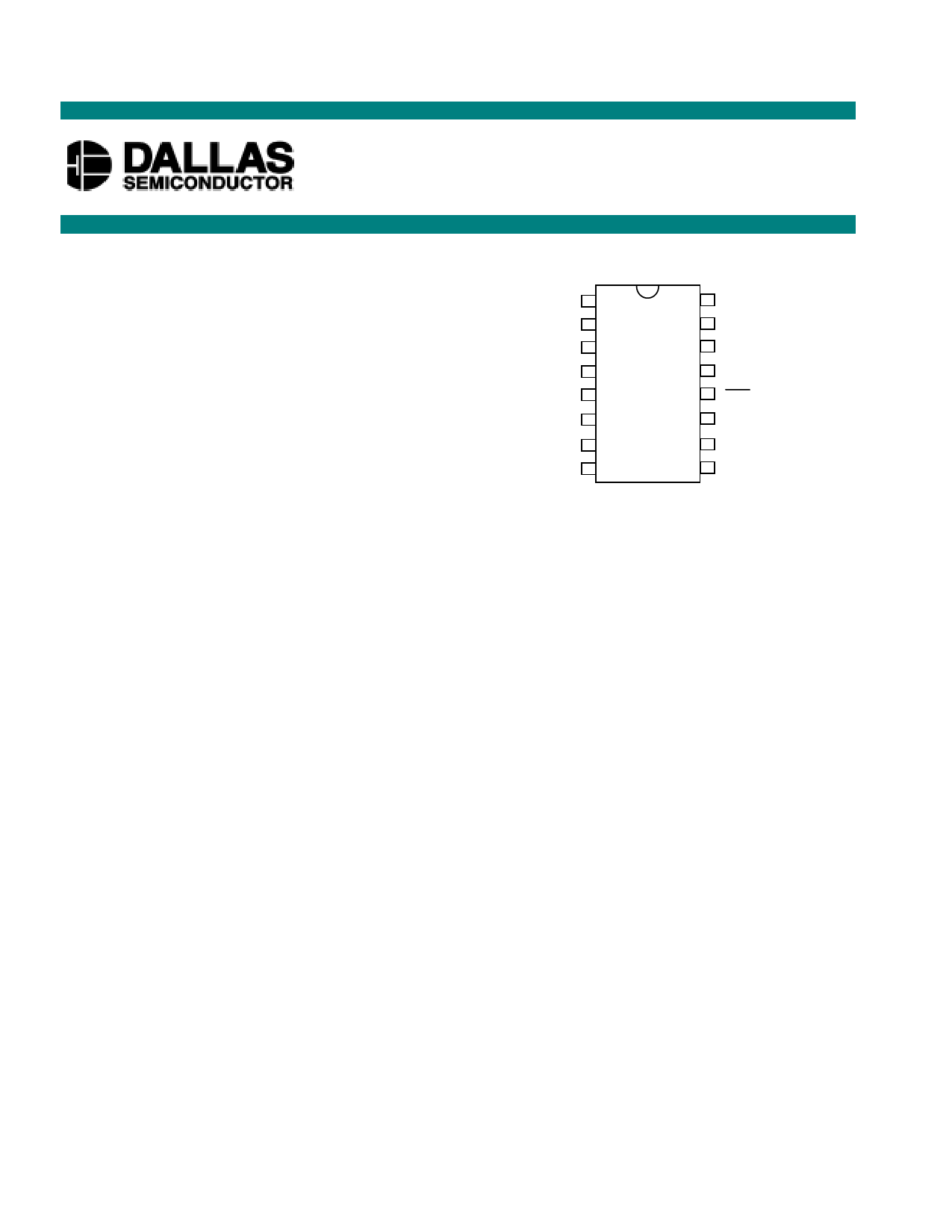

PIN ASSIGNMENT

DJA 1

RPOS 2

RNEG 3

RCLK 4

BDS 5

TEST 6

XTAL OUT 7

VSS 8

16 VDD

15 RRPOS

14 RRNEG

13 RRCLK

12 RST

11 BL

10 XTAL2

9 XTAL1

ORDERING INFORMATION

DS2188

16 Pin dip (0ºC-F70ºC)

DS2188S 16 Pin SOIC (0º-+70ºC)

DS2188N 16 Pin dip (-40ºC-+85ºC)

DS2188SN 16 Pin SOIC (-40ºC-+85-ºC)

DESCRIPTION

The DS2188 T1/CEPT Jitter Attenuator Chip contains a 128 X 2-bit buffer which, in conjunction with an

external 4X crystal, is used to attenuate the incoming jitter present in clock and data. The device meets all

of the latest applicable specifications including those outlined in TR 62411 (Accunet* T1.5 Service

Description and Interface Specifications, December 1990), TR-TSY-000170 (Digital Cross-Connect

System Requirements and Objectives, November 1985), and the CCITT Recommendations G.735 and

G.742. The DS2188 is compatible with the DS2180A T1/ISDN Primary Rate Transceiver and DS2181A

CEPT Transceiver and is the companion to the DS2187 T1/CEPT Receive Line Interface and DS2186

T1/CEPT Transmit Line Interface. It can also be used in conjunction with the DS2190 T1 Network

Interface Unit.

OVERVIEW

The RCLK input is fed to a 128 x 2-bit FIFO where it drives the write pointer for the positive (RPOS) and

negative (RNEG) data. The read pointer of the FIFO and RRCLK is generated by dividing the frequency

of the crystal connected to XTAL1 and XTAL2 by four. The frequency of the crystal is adjusted by a

DPLL to the long-term average frequency of RCLK. As long as the jitter present at RCLK is less than

120 unit intervals peak-to-peak (UIpp), then the FIFO buffer will be able to absorb the incoming jitter and

it will be attenuated in accordance with TR 62411 (December 1990). In this situation, the BL (Buffer

Limit) pin will remain low. Figures 1 and 2 illustrate the DS2188 Jitter Attenuator performance.

If the incoming jitter has excursions greater than 120 UIpp, then the crystal is adjusted to track the short-

term frequency variations of the incoming signal so that there is no loss of data. This adjustment is

accomplished by dividing the 4X crystal by either 3 ½ or 4 ½ instead of 4. When the incoming jitter is

1 of 10

100600