MC12202M Просмотр технического описания (PDF) - Motorola => Freescale

Номер в каталоге

Компоненты Описание

производитель

MC12202M Datasheet PDF : 12 Pages

| |||

MC12202

For FC = HIGH:

fr lags fp in phase OR fp>fr in frequency

When the phase of fr lags that of fp or the frequency of fp is greater than fr, the φP output will remain in a HIGH state while the φR

output will pulse from LOW to HIGH. The output pulse will reach a minimum 50% duty cycle under a 180° out of phase condition.

The signal on φR indicates to the VCO to decrease in frequency to bring the loop into lock.

fr leads fp in phase OR fp<fr in frequency

When the phase of fr leads that of fp or the frequency of fp is less than fr, the φR output will remain in a LOW state while the φP

output pulses from HIGH to LOW. The output pulse will reach a minimum 50% duty cycle under a 180° out of phase condition.

The signal on φP indicates to the VCO to increase in frequency to bring the loop to lock.

fr = fp in phase and frequency

When the phase and frequency of fr and fp are equal, the output φP will remain in a HIGH state and φR will remain in a LOW state

except for voltage spikes when signals are in phase. This situation indicates that the loop is in lock and the phase comparator will

maintain the loop in its locked state.

When FC = LOW, the operation of the phase comparator is reversed from the above explanation.

For FC = LOW:

fr lags fp in phase OR fp>fr in frequency

When the phase of fr lags that of fp or the frequency of fp is greater than fr, the φR output will remain in a LOW state while the φP

output will pulse from HIGH to LOW. The output pulse will reach a minimum 50% duty cycle under a 180° out of phase condition.

The signal on φP indicates to the VCO to increase in frequency to bring the loop into lock.

fr leads fp in phase OR fp<fr in frequency

When the phase of fr leads that of fp or the frequency of fp is less than fr, the φP output will remain in a HIGH state while the φR

output pulses from LOW to HIGH. The output pulse will reach a minimum 50% duty cycle under a 180° out of phase condition.

The signal on φR indicates to the VCO to decrease in frequency to bring the loop to lock.

fr = fp in phase and frequency

When the phase and frequency of fr and fp are equal, the output φP will remain in a HIGH state and φR will remain in a LOW state

except for voltage spikes when signals are in phase. This situation indicates that the loop is in lock and the phase comparator will

maintain the loop in its locked state.

The FC pin controls not only the phase characteristics, but also controls the fOUT test pin. The FC pin permits the user to monitor

either of the phase comparator input signals, fr or fp, at the fOUT output providing a test mode where the programming of the

dividers and the output of the counters can be checked. When FC is HIGH, fOUT = fr, the programmable reference divider output.

When FC is LOW, fOUT = fp, the programmable divider output.

Hence,

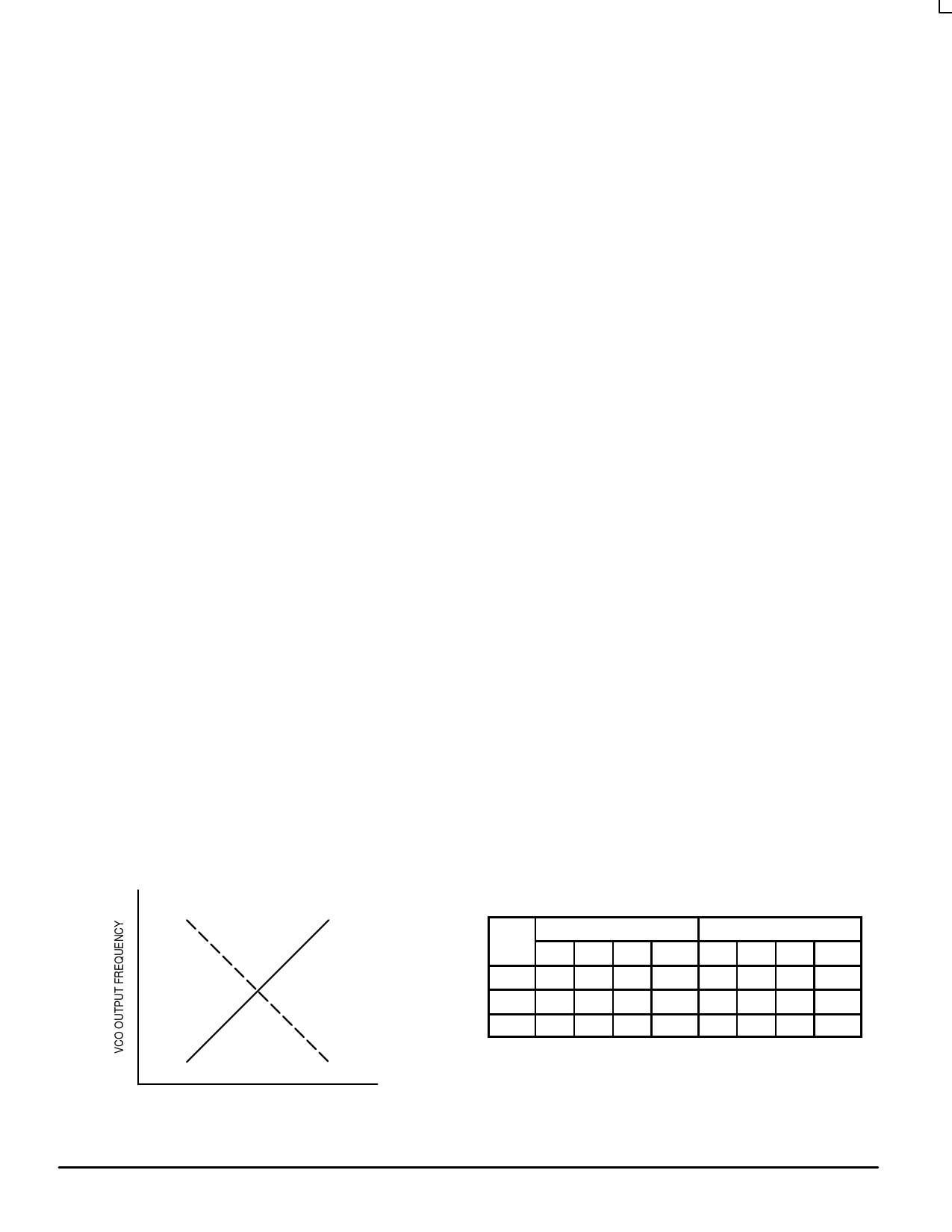

If VCO characteristics are like (1), FC should be set HIGH or OPEN. fOUT = fr

If VCO characteristics are like (2), FC should be set LOW.

fOUT = fp

(1)

(2)

VCO INPUT VOLTAGE

Figure 4. VCO Characteristics

FC = HIGH or OPEN

FC = LOW

Do φR φP fOUT Do φR φP fOUT

fp < fr H L L

fr

L HH

fp

fp > fr L H H

fr

HL L

fp

fp = fr Z L H

fr

ZLH

fp

NOTE: Z = High impedance

When LE is HIGH or Open, BISW has the same characteristics

as Do.

Figure 5. Phase Comparator, Internal Charge Pump, and

fOUT Characteristics

HIPERCOMM

7

BR1334 — Rev 4

MOTOROLA