MT90710 Просмотр технического описания (PDF) - Mitel Networks

Номер в каталоге

Компоненты Описание

производитель

MT90710 Datasheet PDF : 12 Pages

| |||

Preliminary Information

MT90710

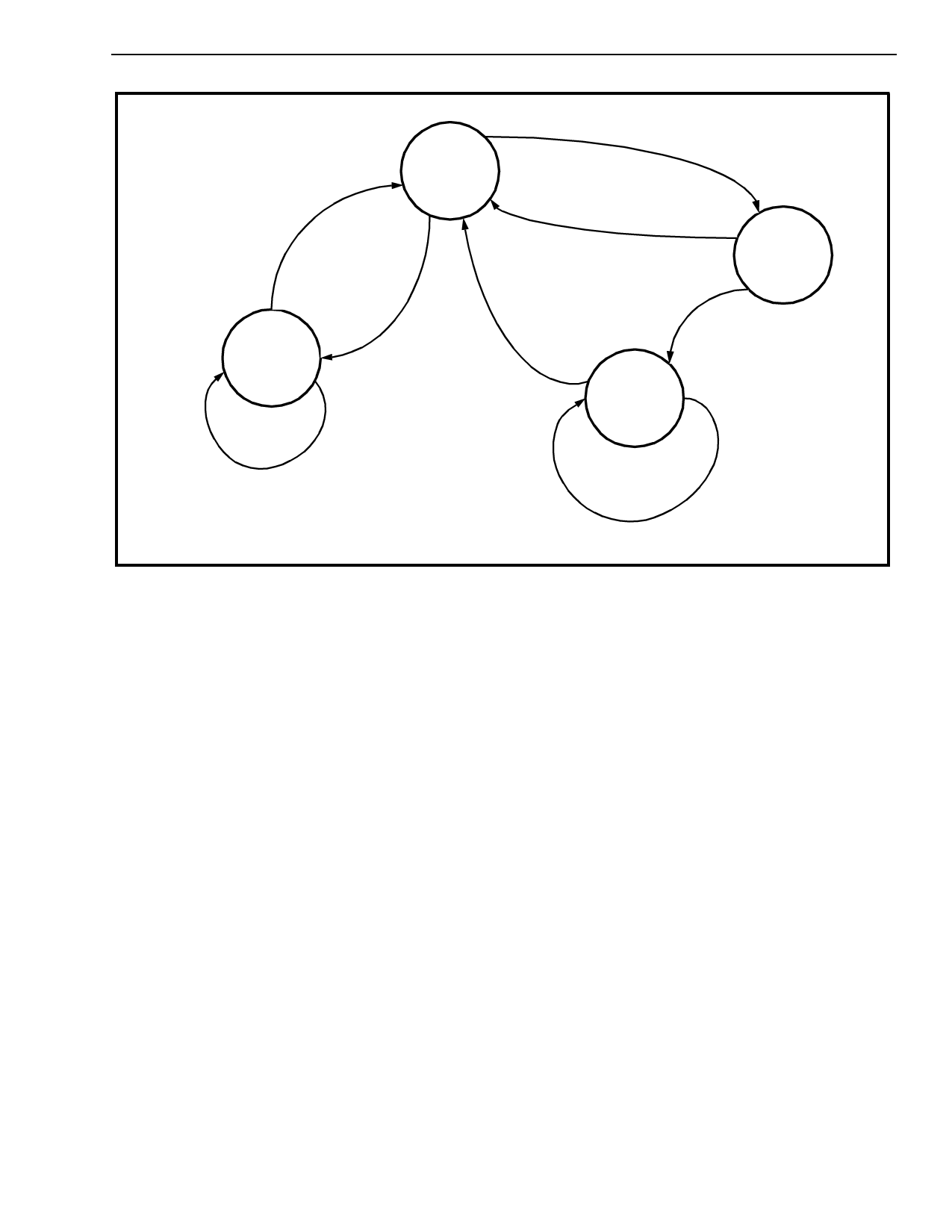

CORRECT SYNC

SET SYNC = FALSE

STATE 1

CORRECT SYNC

SET SYNC = LAST STATE

INCORRECT SYNC

SET SYNC = LAST STATE

STATE 2

STATE 0

INCORRECT SYNC

SET SYNC = FALSE

INCORRECT SYNC

SET SYNC = TRUE

CORRECT SYNC

SET SYNC = TRUE

STATE 3

INCORRECT SYNC

SET SYNC = FALSE

CORRECT SYNC

SET SYNC = TRUE

Figure 5 - State Diagram

Fiber to ST-BUS

When ST6MUX is enabled the STo6A and STo6B

output streams are comprised of the demultiplexed

information received from the fiber link. The received

data is duplicated on two channels since the ST-BUS

channels support twice the bandwidth of the data

from the incoming fiber link. See Table 2.

When ST6MUX is disabled the STi6B and STo6B

ports are not operational. The STi6A and STo6A

ports operate as clear 2.048 MHz links in the same

manner as STi/o links 0 to 5.

approximately a 4 Hz rate when the far-end is out of

synchronization but the near-end is synchronized. If

the near-end is not synchronized this output is

inactive.

The open collector LLED output (pin 70) will cause

an LED, pulled up to +5 volts, to flash at

approximately a 4 Hz rate when the near-end is out

of synchronization.

Checksum Generator

Checksum =

Fiber Loop Synchronization

A receiver is declared in synchronization after

detection of three consecutive frames containing a

valid sync pattern. Once synchronized a receiver will

lose sync if a valid sync pattern is not detected in two

of four consecutive frames (refer to Figure 5).

LED Control

The open collector RLED output (pin 36) will cause

an LED, pulled up to +5 volts, to flash at

255

∑ DATAi + Ci –1

i=1

Where i-1 is the carry out from the previous

operation. The checksum is calculated on all 255

channels except on channel 0 where the frame

synchronization code is transported. During this

channel the previous checksum is stored and the

register initialized for the next calculation.

5-11