DS12887 Просмотр технического описания (PDF) - Dallas Semiconductor -> Maxim Integrated

Номер в каталоге

Компоненты Описание

производитель

DS12887 Datasheet PDF : 19 Pages

| |||

DS12887

unaffected by the lower input voltage. As VCC falls below 3 volts typical, the RAM and timekeeper are

switched over to an internal lithium energy source. The timekeeping function maintains an accuracy of ±1

minute per month at 25°C regardless of the voltage input on the VCC pin.

MOT (Mode Select) – The MOT pin offers the flexibility to choose between two bus types. When

connected to VCC, Motorola bus timing is selected. When connected to GND or left disconnected, Intel

bus timing is selected. The pin has an internal pulldown resistance of approximately 20 kΩ.

SQW (Square Wave Output) – The SQW pin can output a signal from one of 13 taps provided by the

15 internal divider stages of the Real Time Clock. The frequency of the SQW pin can be changed by

programming Register A as shown in Table 1. The SQW signal can be turned on and off using the SQWE

bit in Register B. The SQW signal is not available when VCC is less than 4.25 volts, typically.

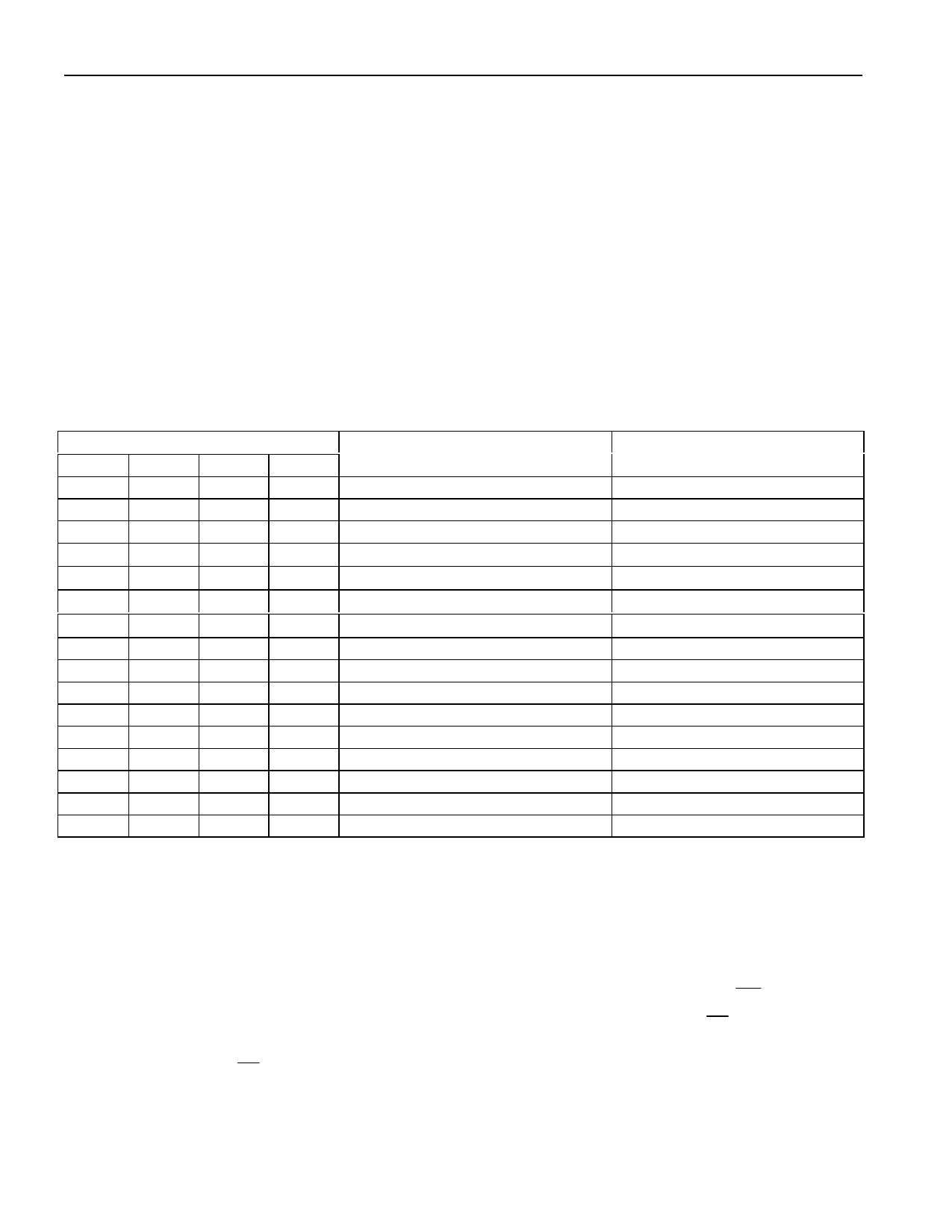

PERIODIC INTERRUPT RATE AND SQUARE

WAVE OUTPUT FREQUENCY Table 1

SELECT BITS REGISTER A

RS3 RS2 RS1 RS0

tPI PERIODIC

INTERRUPT RATE

0

0

0

0

None

0

0

0

1

3.90625 ms

0

0

1

0

7.8125 ms

0

0

1

1

122.070 µs

0

1

0

0

244.141 µs

0

1

0

1

488.281 µs

0

1

1

0

976.5625 µs

0

1

1

1

1.953125 ms

1

0

0

0

3.90625 ms

1

0

0

1

7.8125 ms

1

0

1

0

15.625 ms

1

0

1

1

31.25 ms

1

1

0

0

62.5 ms

1

1

0

1

125 ms

1

1

1

0

250 ms

1

1

1

1

500 ms

SQW OUTPUT

FREQUENCY

None

256 Hz

128 Hz

8.192 kHz

4.096 kHz

2.048 kHz

1.024 kHz

512 Hz

256 Hz

128 Hz

64 Hz

32 Hz

16 Hz

8 Hz

4 Hz

2 Hz

AD0–AD7 (Multiplexed Bidirectional Address/Data Bus) – Multiplexed buses save pins because

address information and data information time-share the same signal paths. The addresses are present

during the first portion of the bus cycle and the same pins and signal paths are used for data in the second

portion of the cycle. Address/data multiplexing does not slow the access time of the DS12887 since the

bus change from address to data occurs during the internal RAM access time. Addresses must be valid

prior to the falling edge of AS/ ALE, at which time the DS12887 latches the address from AD0 to AD6.

Valid write data must be present and held stable during the latter portion of the DS or WR pulses. In a

read cycle the DS12887 outputs 8 bits of data during the latter portion of the DS or RD pulses. The read

cycle is terminated and the bus returns to a high impedance state as DS transitions low in the case of

Motorola timing or as RD transitions high in the case of Intel timing.

AS (Address Strobe Input) – A positive-going address strobe pulse serves to demultiplex the bus. The

falling edge of AS/ALE causes the address to be latched within the DS12887. The next rising edge that

3 of 19