UT1750AR12WCC Просмотр технического описания (PDF) - Aeroflex UTMC

Номер в каталоге

Компоненты Описание

производитель

UT1750AR12WCC Datasheet PDF : 56 Pages

| |||

GENERAL DESCRIPTION

The UT1750AR (figures 1 and 2) is a high performance

monolithic CMOS 16-bit RISC microprocessor that supports

the complete MIL-STD-1750A Instruction Set Architecture

(ISA). Underlying the MIL-STD-1750A support is a high-

performance RISC that provides MIL-STD-1750A emulation

capability. Developed to provide effective real-time avionics

processing, the high performance of the native RISC machine

is available to the MIL-STD-1750A systems designer through

the MIL-STD-1750A Built-In-Function (BIF) opcode.

The UT1750AR is the first member of a family of high-

performance MIL-STD-1750 processors and support

peripherals from UTMC.

PRODUCT DESCRIPTION

The UTMC UT1750AR operates in its native RISC language

mode or MIL-STD-1750A ISA mode. As a MIL-STD-1750A

microprocessor, the UT1750AR requires 8K x 16 of ROM to

map the MIL-STD-1750A instruction set into the native RISC

machine language instructions. Each MIL-STD-1750A opcode

has a unique RISC code macro in the external ROM. The

UT1750AR executes the corresponding resident RISC code

macro to perform the MIL-STD-1750A instruction

requirements. When in this mode and operating with a 12 MHz

clock, the UT1750AR can throughput 600 KIPS using the DAIS

mix (800 KIPS @ 16 MHz).

The native RISC language mode is available to the user when

the UT1750AR is operating as MIL-STD-1750A processor

through MIL- STD-1750A’s Built-In Function (BIF) opcode.

When operating as a RISC processor, the UT1750AR executes

most RISC instructions in two clock cycles. Thus, a 12 MHz

operating clock frequency provides up to 6 MIPS of RISC

throughput (8 MIPS @16 MHz). This high execution rate, along

with its efficient architecture, make the RISC mode especially

effective in applications requiring real-time processing.

The architecture of the UT1750AR is based around 20 user-

accessible, 16-bit general purpose registers providing the

programmer with extensive register support. The UT1750AR’s

flexibility is enhanced by its ability to concatenate the 16-bit

registers into ten 32-bit registers. In addition, all registers are

available for use as either the source or the destination for any

register operation.

The UT1750AR fully supports multiprocessor, DMA, and

complex bus arbitration for managing the system bus and

preventing bus contention. Bus control passes among bus

masters operating on the same bus. The bus masters can be

several UT1750ARs or any other device requiring Direct

Memory Access, such as a MIL-STD-1553B interface.

The UT1750AR supports 16 levels of vectored interrupts. Ten

of these are external interrupts, eight of which are user-

definable. All 16 interrupt levels are prioritized and serviced in

order of priority.

When used as a MIL-STD-1750A microprocessor, the

UT1750AR’s instruction set supports 16-bit fixed-point single-

precision and 32-bit fixed-point double-precision data formats.

Also, the UT1750AR can emulate 32-bit floating-point and 48-

bit floating-point extended-precision data in two’s complement

representation.

In its native RISC mode, the UT1750AR’s three basic

instruction formats support 16-bit and 32-bit instructions. The

formats are Register-to-Register, Register-to-Literal, and

Register-to-Long-Immediate instructions.

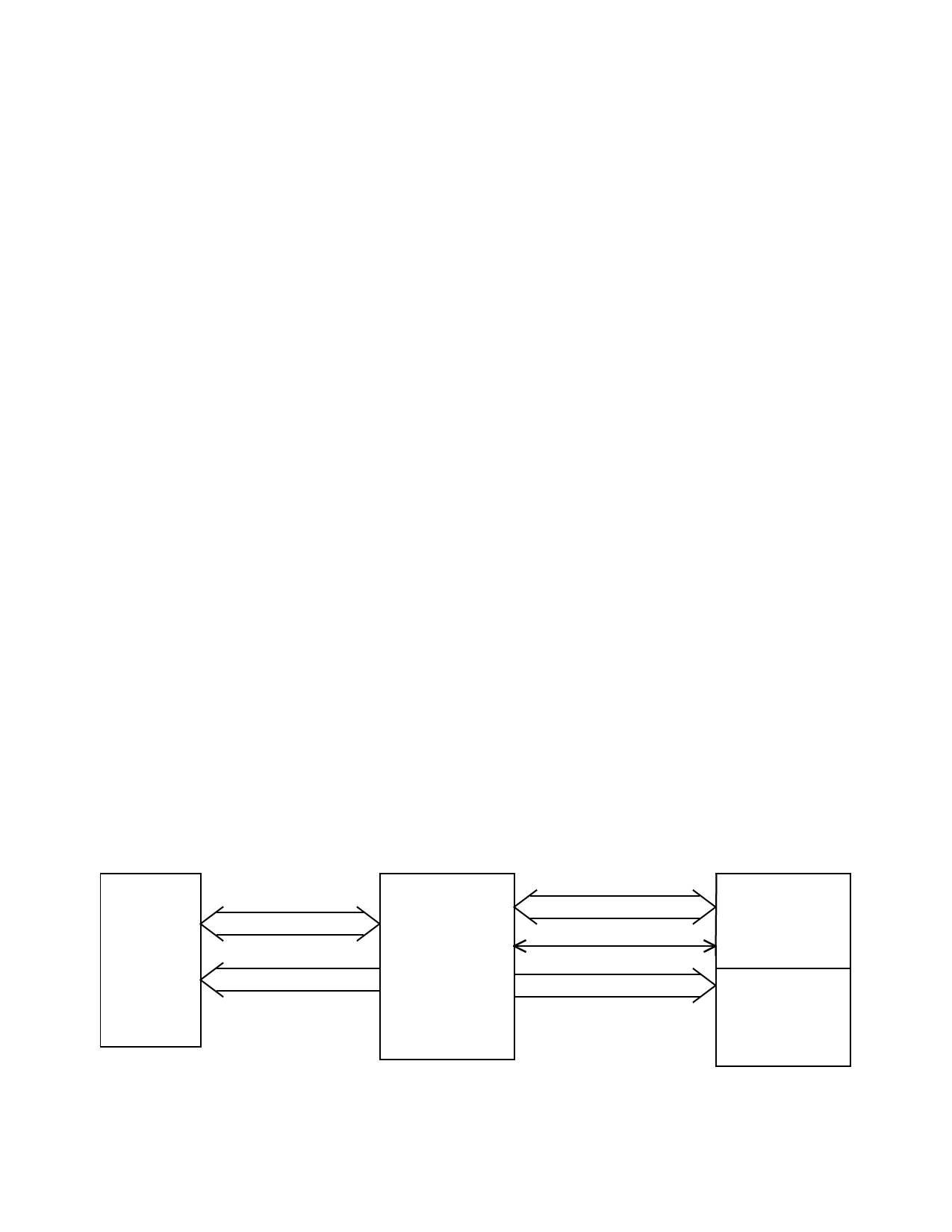

Figure 3 shows the UT1750AR’s general system architecture,

its emulation ROM, instruction and data memory, and the

system interface. The emulation ROM is isolated from the

system; only the UT1750AR microprocessor accesses it.

EMULATION

ROM

(8K X 16)

RISC DATA

16

RISC ADDRESS

16

UT1750AR

OPERAND DATA

16

CONTROL

OPERAND ADDRESS

16

MIL-STD-1750A

MEMORY

INSTRUCTIONS

DATA

Figure 3. UT1750AR MIL-STD-1750A General System Architecture

3