UT1750AR12WCC Просмотр технического описания (PDF) - Aeroflex UTMC

Номер в каталоге

Компоненты Описание

производитель

UT1750AR12WCC Datasheet PDF : 56 Pages

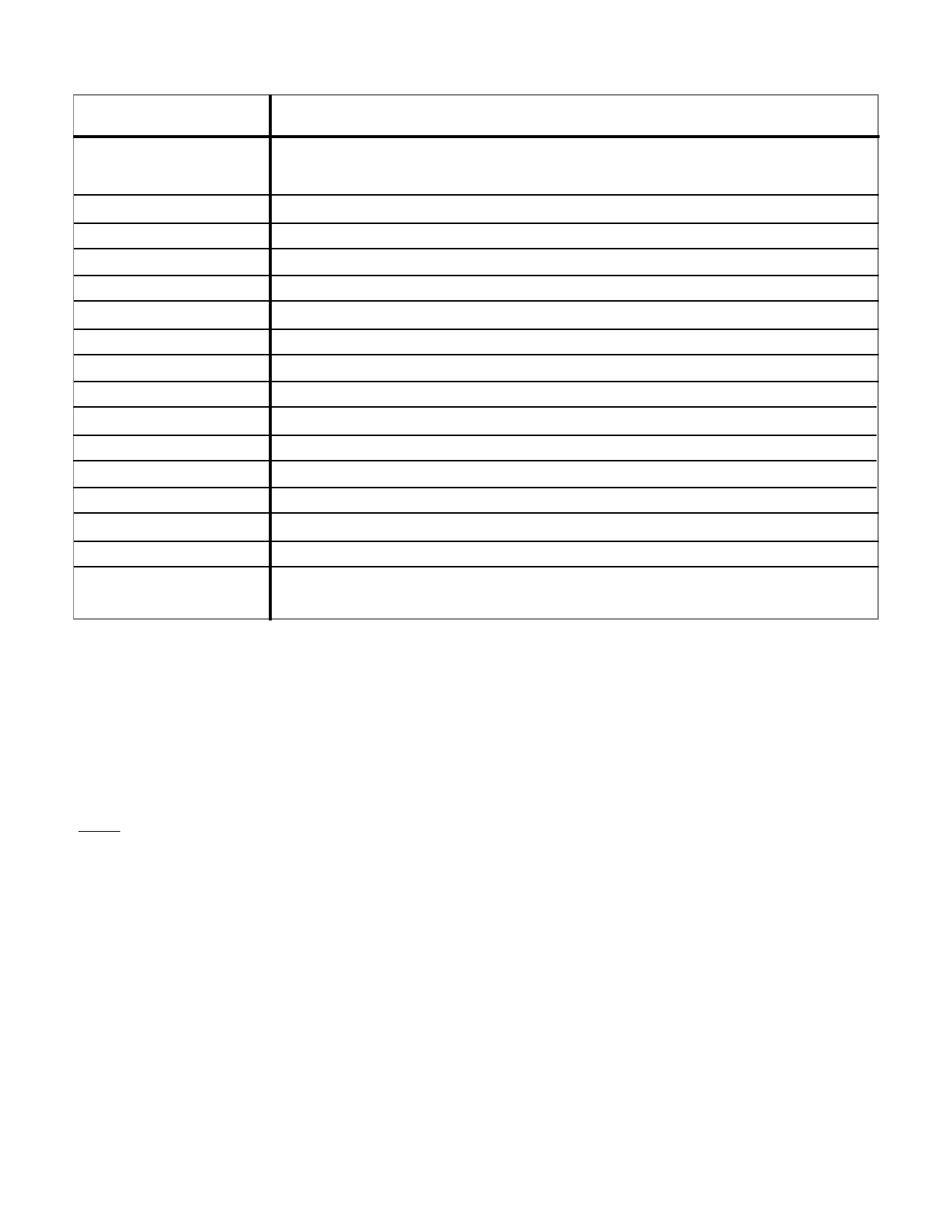

| |||

INTERRUPT

NUMBER

0

(Highest

Priority)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

(Lowest

Priority)

Table 1. Interrupt Definitions

DESCRIPTION

Power-Down Interrupt.Cannot be masked or disabled.

Machine Error. Cannot bedisabled.

INT0. External user interrupt.

Floating-point overflow.

Fixed-point overflow.

Branch Executive. Cannot be masked or disabled.

Floating-point underflow.

1750 Timer A (If implemented).

INT1. External user interrupt.

1750 Timer B (If implemented).

INT2. External user interrupt.

INT3. External user interrupt.

Input/Output level 1.

INT4. External user interrupt.

Input/Output level 2.

INT5. External user interrupt.

Interrupt Operation and Exception Handling

The UT1750AR supports 16 levels of interrupts (table 1). Eight

(INT0 through INT5, IOL1, and IOL2) of the 16 interrupts are

externally available for system use when the UT1750AR

operates in the RISC mode. The UT1750AR internally defines

the remaining interrupts for specific purposes. The UT1750AR

internally prioritizes the 16 interrupts; Interrupt 0 (Power Down

Interrupt) has the highest priority, and Interrupt 15 (INT5) has

the lowest. Interrupts 0 and 5 are cleared when a Master Reset

(MRST) is asserted.

All the UT1750AR’s 16 interrupts are edge-triggered, except

Interrupt 3 (Floating-Point Overflow), Interrupt 5 (Executive

Call), and Interrupt 6 (Floating-Point Underflow). If any one of

the 16 interrupts becomes active, the UT1750AR latches the bit

corresponding to the active interrupt into the Pending Interrupt

Register (PI). The program can now read the PI to determine

which of the 16 interrupts has occurred.

When the UT1750AR is operating in the RISC mode and an

interrupt alters the RISC program flow, the UT1750AR first

saves the present value of the Instruction Counter (IC) in the

Instruction Counter Save Register (ICS), and then disables the

interrupts. The UT1750AR then loads the IC with the memory

location (table 2) corresponding to that interrupt.

When programming the UT1750AR, the ICS must be read with

an Input instruction before the interrupts are re-enabled or before

executing a CALL or JC (BR) instruction to assure that the

return address in the ICS is not overwritten. The CALL

instruction also saves the IC in the ICS and overwrites the

interrupt return address with the CALL return address.

Similarly, if the interrupts are re-enabled before the interrupt

return address is read from the ICS, the occurrence of a new

interrupt causes the old return address to be overwritten.

Therefore, for CALL instructions the system programmer

should reserve register pair XR16 for ICS storage; for interrupts,

the system programmer should reserve register pair XR18 for

ICS storage. When nested CALLS or interrupts are encountered,

the address values stored in register pairs XR16 and XR18,

respectively, must be stored in system memory to provide the

UT1750AR with full return information.

26