EPM3032A Просмотр технического описания (PDF) - Altera Corporation

Номер в каталоге

Компоненты Описание

производитель

EPM3032A Datasheet PDF : 46 Pages

| |||

MAX 3000A Programmable Logic Device Family Data Sheet

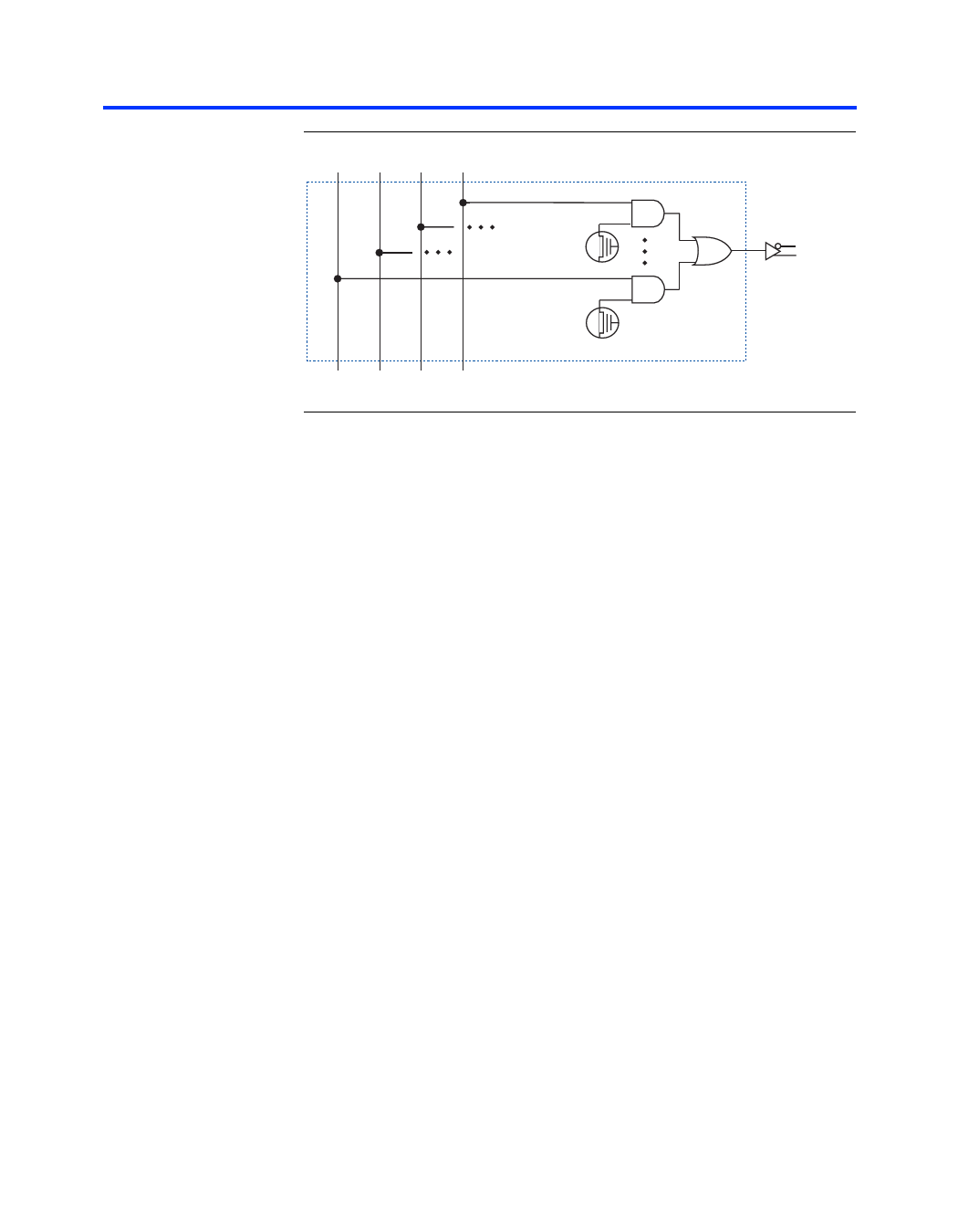

Figure 5. MAX 3000A PIA Routing

To LAB

PIA Signals

While the routing delays of channel–based routing schemes in masked or

FPGAs are cumulative, variable, and path–dependent, the MAX 3000A

PIA has a predictable delay. The PIA makes a design’s timing

performance easy to predict.

I/O Control Blocks

The I/O control block allows each I/O pin to be individually configured

for input, output, or bidirectional operation. All I/O pins have a tri–state

buffer that is individually controlled by one of the global output enable

signals or directly connected to ground or VCC. Figure 6 shows the I/O

control block for MAX 3000A devices. The I/O control block has 6 or

10 global output enable signals that are driven by the true or complement

of two output enable signals, a subset of the I/O pins, or a subset of the

I/O macrocells.

Altera Corporation

11