S24022 Просмотр технического описания (PDF) - Summit Microelectronics

Номер в каталоге

Компоненты Описание

производитель

S24022

S24022 Datasheet PDF : 14 Pages

| |||

S24022/S24023

Read/Write Bit

The last bit of the data stream defines the operation to be

performed. When set to “1,” a read operation is selected;

when set to “0,” a write operation is selected.

While the internal write cycle is in progress, the S24022/

23 inputs are disabled, and the device will not respond to

any requests from the master. Refer to Figure 5 for the

address, ACKnowledge and data transfer sequence.

WRITE OPERATIONS

The S24022/23 allows two types of write operations: byte

write and page write. The byte write operation writes a

single byte during the nonvolatile write period (tWR). The

page write operation allows up to 16 bytes in the same

page to be written during tWR.

Byte WRITE

After the slave address is sent (to identify the slave

device, and a read or write operation), a second byte is

transmitted which contains the 8 bit address of any one of

the 256 words in the array.

Upon receipt of the word address, the S24022/23 re-

sponds with an ACKnowledge. After receiving the next

byte of data, it again responds with an ACKnowledge. The

master then terminates the transfer by generating a

STOP condition, at which time the S24022/23 begins the

internal write cycle.

Page WRITE

The S24022/23 is capable of a 16-byte page write opera-

tion. It is initiated in the same manner as the byte-write

operation, but instead of terminating the write cycle after

the first data word, the master can transmit up to 15 more

bytes of data. After the receipt of each byte, the S24022/

23 will respond with an ACKnowledge.

The S24022/23 automatically increments the address for

subsequent data words. After the receipt of each word,

the low order address bits are internally incremented by

one. The high order bits of the address byte remain

constant. Should the master transmit more than 16 bytes,

prior to generating the STOP condition, the address

counter will “roll over,” and the previously written data will

be overwritten. As with the byte-write operation, all inputs

are disabled during the internal write cycle. Refer to

Figure 5 for the address, ACKnowledge and data transfer

sequence.

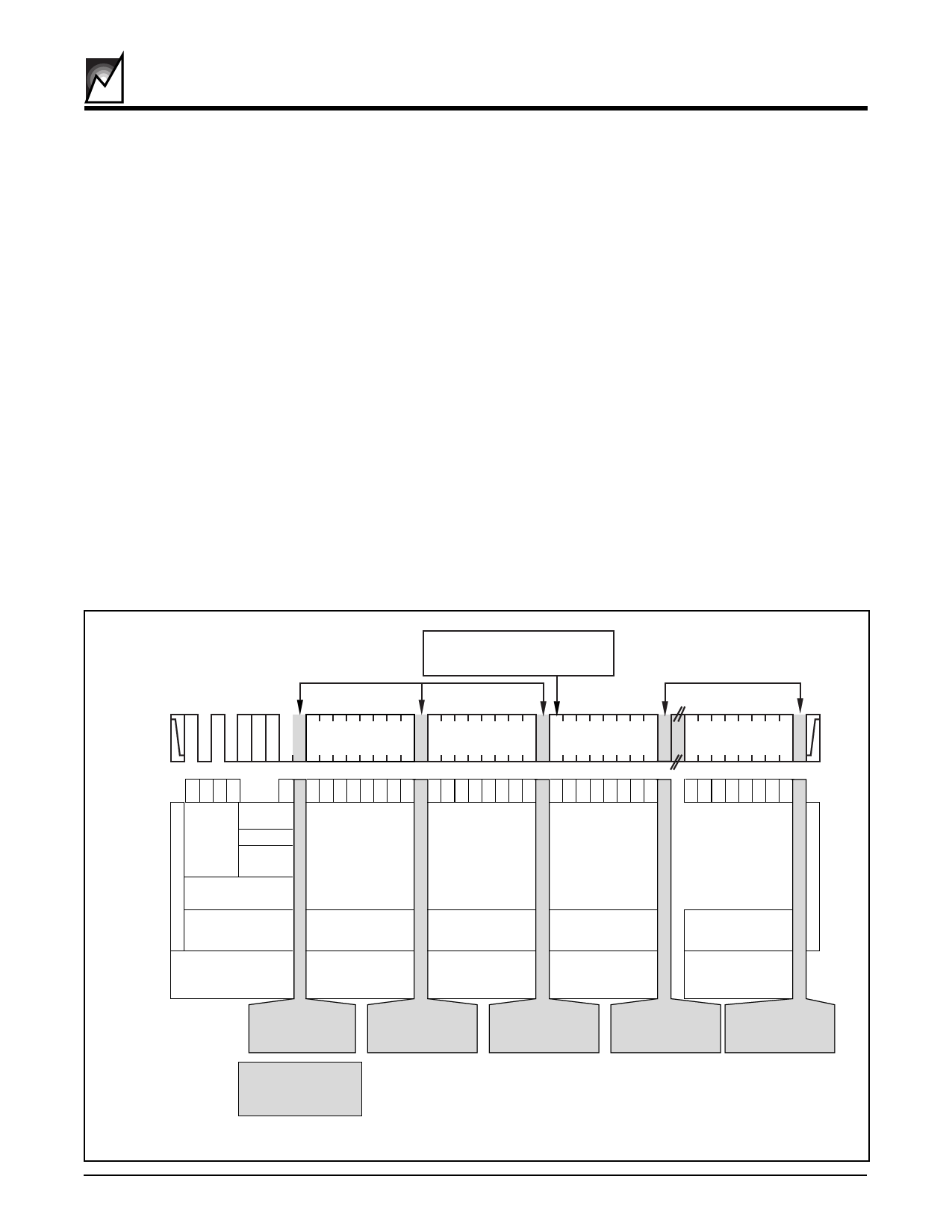

Acknowledges Transmitted from

24022/23 to Master Receiver

If single byte-write only,

Stop bit issued here.

Acknowledges Transmitted from

24022/23 to Master Receiver

SDA

Bus

Activity

A

XXXRC

WK

A

A

A

C Data Byte n C Data Byte n+1 C

K

K

K

1010

0

AAAAAAAA

76543210

DDDDDDDD

76543210

DDDDDDDD

76543210

S

T Device

A Type

R

T

Address Read/Write

0= Write

A

Data Byte n+15 C

K

DDDDDDDD

76543210

S

T

O

P

Slave Address

Master Sends Read

Request to Slave

Master Writes Word

Address to Slave

Master Writes

Data to Slave

Master Writes

Data to Slave

Master Writes

Data to Slave

Master Transmitter

to

Slave Receiver

Master Transmitter

to

Slave Receiver

Master Transmitter

to

Slave Receiver

Master Transmitter

to

Slave Receiver

Master Transmitter

to

Slave Receiver

Slave Transmitter

to

Master Receiver

Slave Transmitter

to

Master Receiver

Slave Transmitter

to

Master Receiver

Slave Transmitter

to

Master Receiver

Slave Transmitter

to

Master Receiver

Shading Denotes

24022/23

SDA Output Active

2010 ILL8 1.2

FIGURE 5. PAGE/BYTE WRITE MODE

2010 1.4 5/3/98

5