SPT9712 Просмотр технического описания (PDF) - Fairchild Semiconductor

Номер в каталоге

Компоненты Описание

производитель

SPT9712 Datasheet PDF : 7 Pages

| |||

ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)1 25 °C

Supply Voltages

Output Currents

Negative Supply Voltage (VEE) .............................. –7 V Internal Reference Output Current .................... 500 µA

A/D Ground Voltage Differential ........................... 0.5 V Control Amplifier Output Current ..................... ±2.5 mA

Input Voltages

Digital Input Voltage

(D1–D12, Latch Enable) ............................... 0 V to VEE

Control Amp Input Voltage Range ............... 0 V to –4 V

Reference Input Voltage Range (VREF) ........ 0 V to VEE

Temperature

Operating Temperature .......................... –40 to +85 °C

Junction Temperature ...................................... +150 °C

Lead, Soldering (10 seconds) ......................... +300 °C

Storage ................................................ –65 to +150 °C

Note: 1. Operation at any Absolute Maximum Rating is not implied. See

Electrical Specifications for proper nominal applied conditions

in typical applications.

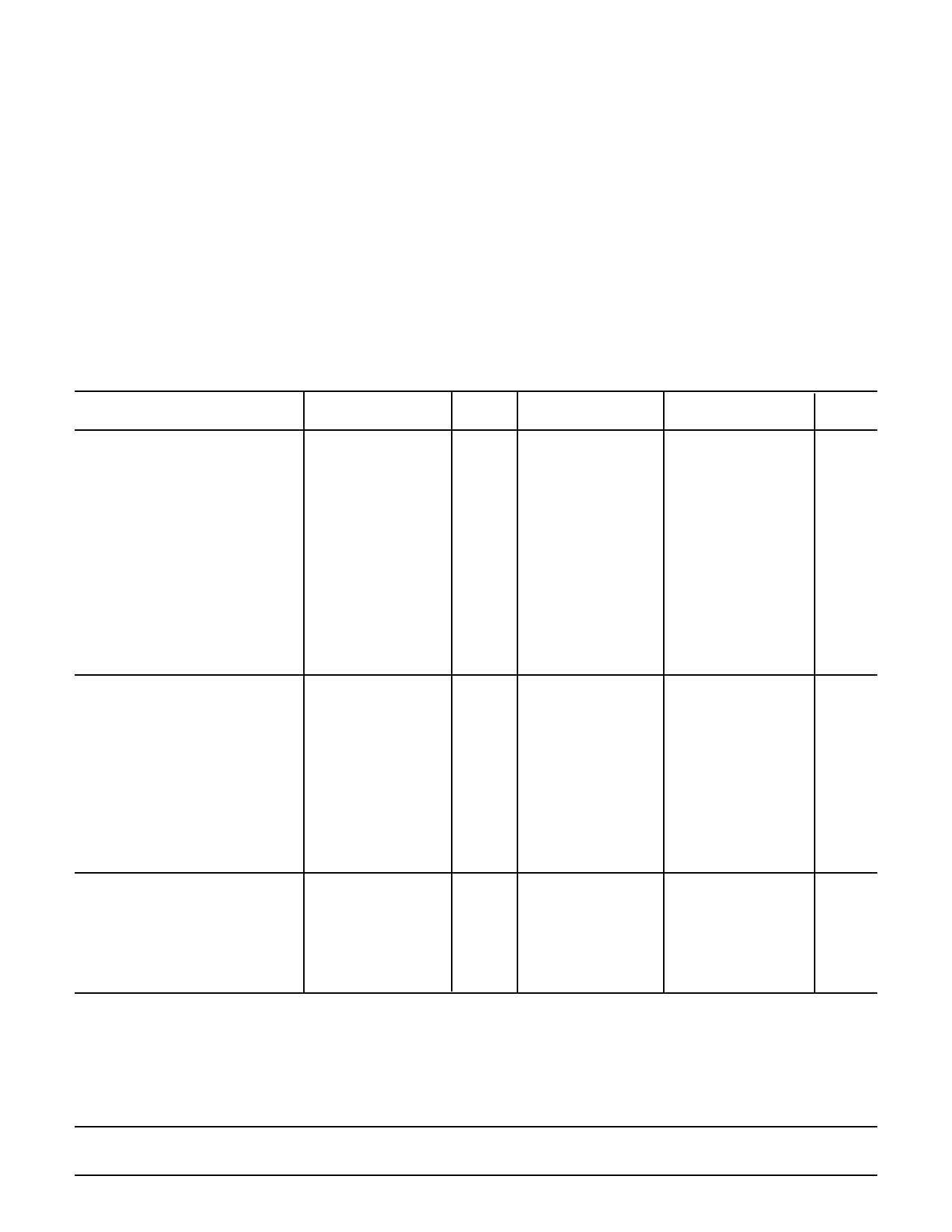

ELECTRICAL SPECIFICATIONS

TA = TMIN – TMAX, VEE = –5.2 V, RSet = 7.5 kΩ, Control Amp In = Ref Out, VOUT = 0 V, unless otherwise specified.

PARAMETERS

DC Performance

Resolution

Differential Linearity

Differential Linearity

Integral Linearity

Integral Linearity

Output Capacitance

Gain Error1

Gain Error Tempco

Zero-Scale Offset Error

Offset Drift Coefficient

Output Compliance Voltage

Equivalent Output Resistance

TEST

CONDITIONS

Max at Full Temp.

Best Fit

Max at Full Temp.

+25 °C

+25 °C

Full Temp.

Full Temp.

+25 °C

Full Temp.

Full Temp.

+25 °C

+25 °C

TEST

SPT9712A

SPT9712B

LEVEL MIN TYP MAX MIN TYP MAX

12

12

I

±0.5 ±0.75

±1.0 ±1.25

VI

±1.5

±2.0

I

±0.75 ±1.0

±1.0 ±1.5

VI

±1.75

±2.0

V

10

10

I

1.0 5.0

1.0 5.0

VI

8.0

8.0

V

150

150

I

0.5 2.5

0.5 2.5

VI

5.0

5.0

V

0.01

0.01

IV –1.2

+2.0 –1.2

+2.0

IV

0.8 1.0 1.2

0.8 1.0 1.2

Dynamic Performance

Conversion Rate

Settling Time tST2

Output Propagation Delay tD3

Glitch Energy4

Full Scale Output Current5

Spurious-Free Dynamic Range6

1.23 MHz; 10 MWPS

5.055 MHz; 20 MWPS

10.1 MHz; 50 MWPS

16 MHz; 40 MWPS

Rise Time / Fall Time

+25 °C

+25 °C

+25 °C

+25 °C

+25 °C

+25 °C

2 MHz Span

2 MHz Span

2 MHz Span

10 MHz Span

RL = 50 Ω

IV

100

V

13

V

1

V

15

V

20.48

V

70

V

68

V

68

V

68

V

2

100

13

1

15

20.48

70

68

68

68

2

Power Supply Requirements

Negative Supply Voltage

IV –5.46 –5.2 –4.94 –5.46 –5.2 –4.94

Negative Supply Current (–5.2 V) +25 °C

I

115 140

115 140

Full Temp

VI

148

148

Nominal Power Dissipation

V

600

600

Power Supply Rejection Ratio

±5% of VEE

I

30 100

30 100

External Ref, +25 °C

UNITS

Bits

LSB

LSB

LSB

LSB

pF

% FS

% FS

PPM/°C

µA

µA

µA/°C

V

kΩ

MWPS

ns

ns

pV-s

mA

dBc

dBc

dBc

dBc

ns

V

mA

mA

mW

µA/V

1Gain is measured as a ratio of the full-scale current to ISet. The ratio is nominally 128.

2Measured as voltage at mid-scale transition to ±0.024%; RL=50 Ω.

3Measured from the rising edge of Latch Enable to where the output signal has left a 1 LSB error band.

4Glitch is measured as the largest single transient.

5Calculated using IFS = 128 x (Control Amp In / RSet)

6SFDR is defined as the difference in signal energy between the fundamental and worst case spurious frequencies in the output spectrum window,

which is centered at the fundamental frequency and covers the indicated span.

SPT9712

2

2/15/01