HSP45102(1999) Просмотр технического описания (PDF) - Intersil

Номер в каталоге

Компоненты Описание

производитель

HSP45102 Datasheet PDF : 7 Pages

| |||

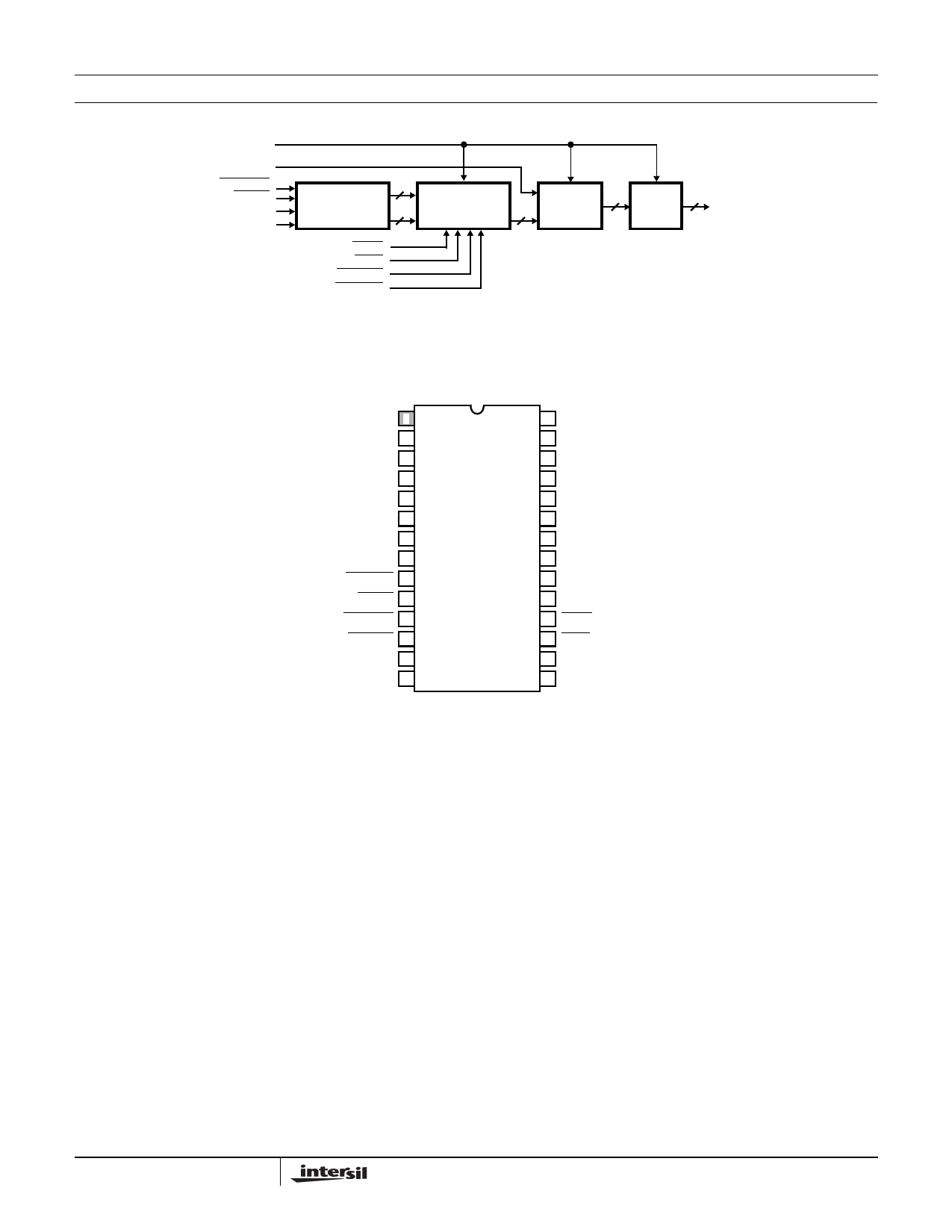

Pinout

HSP45102

28 LEAD PDIP, 28 LEAD SOIC

TOP VIEW

OUT6 1

OUT7 2

OUT8 3

OUT9 4

OUT10 5

OUT11 6

GND 7

VCC 8

SEL_L/M 9

SFTEN 10

MSB/LSB 11

ENPHAC 12

SD 13

SCLK 14

28 OUT5

27 OUT4

26 OUT3

25 OUT2

24 OUT1

23 OUT0

22 VCC

21 GND

20 P0

19 P1

18 LOAD

17 TXFR

16 CLK

15 GND

Pin Description

NAME

TYPE

DESCRIPTION

VCC

GND

+5V power supply pin.

Ground

P0-1

I

Phase modulation inputs (become active after a pipeline delay of four clocks). A phase shift of 0, 90,

180, or 270 degrees can be selected as shown in Table 1.

CLK

I

NCO clock. (CMOS level)

SCLK

I

This pin clocks the frequency control shift register.

SEL_L/ M

I

A high on this input selects the least significant 32 bits of the 64-bit frequency register as the input to

the phase accumulator; a low selects the most significant 32 bits.

SFTEN

I

The active low input enables the shifting of the frequency register.

MSB/ LSB

I

This input selects the shift direction of the frequency register. A low on this input shifts in the data LSB

first; a high shifts in the data MSB first.

ENPHAC

I

This pin, when low, enables the clocking of the Phase Accumulator. This input has a pipeline delay of

four clocks.

SD

I

Data on this pin is shifted into the frequency register by the rising edge of SCLK when SFTEN is low.

TXFR

I

This active low input is clocked onto the chip by CLK and becomes active after a pipeline delay of four

clocks. When low, the frequency control word selected by SEL_L/M is transferred from the frequency

register to the phase accumulator’s input register.

LOAD

I

This input becomes active after a pipeline delay of five clocks. When low, the feedback in the phase

accumulator is zeroed.

OUT0-11

O

Output data. OUT0 is LSB. Unsigned.

All inputs are TTL level, with the exception of CLK.

Overline designates active low signals.

3-196