MT89L86AN Просмотр технического описания (PDF) - Mitel Networks

Номер в каталоге

Компоненты Описание

производитель

MT89L86AN Datasheet PDF : 40 Pages

| |||

MT89L86

Advance Information

Pin Description (continued)

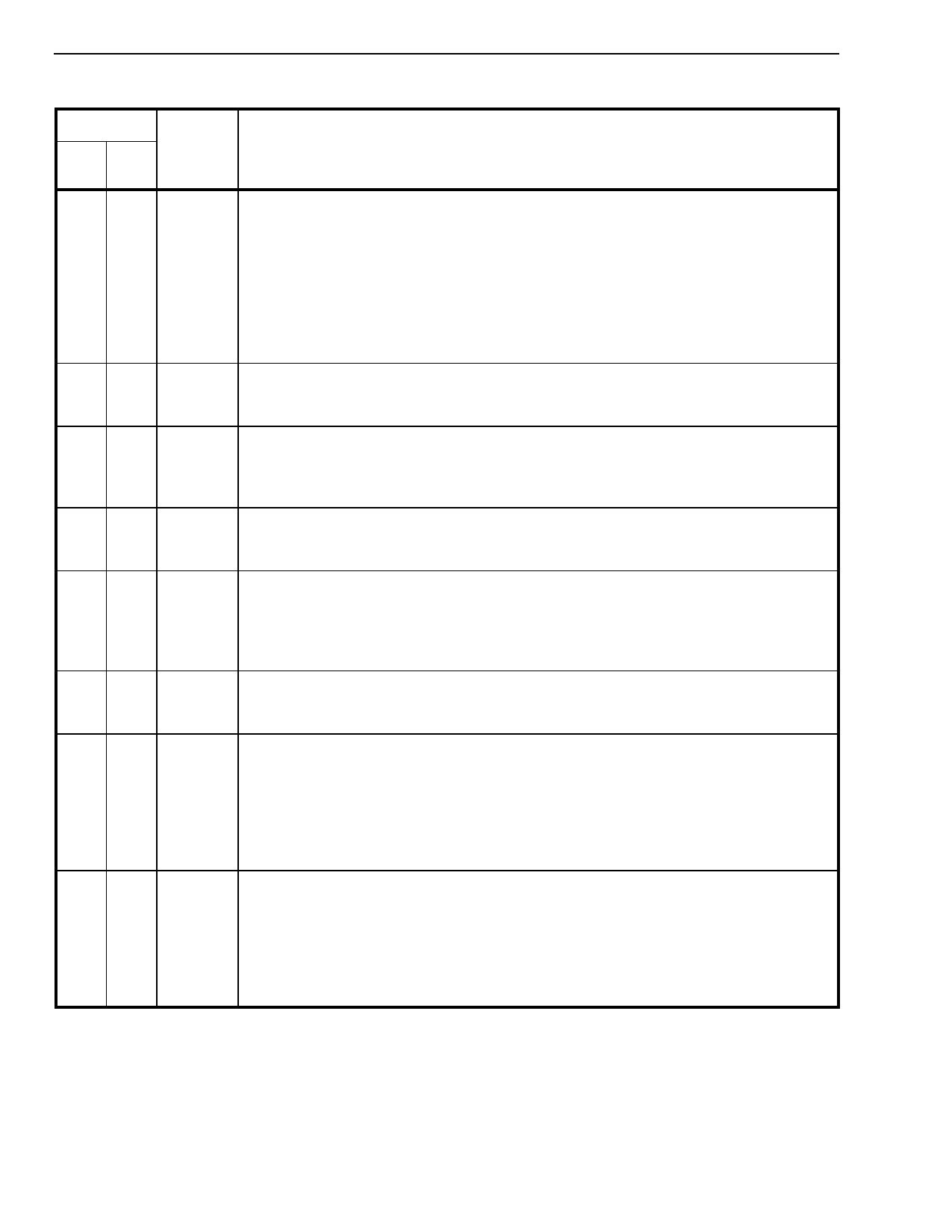

Pin #

44 48

PLCC SSOP

Name

Description

36 39 STo6/A6 ST-BUS Output 6/Address 6 input (Three-state output/input). The function of this

pin is determined by the switching configuration enabled. If non-multiplexed CPU bus is

used along with a higher data rate employing 8.192 or 4.096 Mb/s, this pin provides the

A6 address input function. For 2.048 Mb/s applications or when the multiplexed CPU

bus interface is selected, this pin assumes STo6 function. See Tables 1, 2, 6 & 7 for

more details.

Note that for applications where both A6 input and STo6 output are required

simultaneously (e.g., 4.096 to 2.048 Mb/s or 8.192 to 2.048 Mb/s rate conversion

applications), the A6 input should be connected to pin STi6/A6.

37-39 40-42

41-43 44-46

44 47

STo5-0

ODE

ST-BUS Outputs 5 to 0 (Three-state Outputs). Serial data output streams. These

serial streams may be composed of 32, 64 and 128 channels at data rates of 2.048,

4.096 or 8.192 Mbit/s, respectively.

Output Drive Enable (5V-tolerant Input). This is the output enable input for the STo0

to STo9 serial outputs. If this input is low STo0-9 are high impedance. If this input is

high each channel may still be set to high impedance by using per-channel control bits

in Connect Memory High.

1 48 CSTo Control ST-BUS Output (Output). This is a 2.048 Mb/s output containing 256 bits per

frame. The level of each bit is determined by the CSTo bit in the Connect Memory high

locations.

6

6 AS/ALE Address Strobe or Latch Enable (5V-tolerant Input). This input is only used if

multiplexed bus is selected via the IM input pin.

The falling edge of this signal is used to sample the address into the address latch

circuit. When the non-multiplexed bus interface is selected, this input is not required

and should be connected to ground.

18 19

IM CPU Interface Mode (5V-tolerant Input). If HIGH, this input configures the MT89L86

in the multiplexed microprocessor bus mode. When this input pin is connected to

ground, the MT89L86 assumes non-multiplexed CPU interface.

28 30 STi15/ ST-BUS Input 15 / ST-BUS Output 9 (Input/three-state output). This pin is only used

STo9 if multiplexed CPU bus is selected. If 16-input x 8-output switching configuration is

enabled in the SCB bits (IMS register), this pin is an input receiving serial ST-BUS

stream 15 at a data rate of 2.048 Mbit/s.

If Stream Pair Selection capability is enabled (see switching configuration section), this

pin is the ST-BUS stream 9 output.

When non-multiplexed bus structure is used, this pin should be connected to ground.

40 43 STi14/ ST-BUS Input 14 / ST-BUS Output 8 (Input/three-state output). This pin is only used

STo8 if multiplexed CPU bus is selected. If 16-input x 8-output switching configuration is

enabled in the SCB bits (IMS register), this pin is an input that receives serial ST-BUS

stream 14 at a data rate of 2.048 Mbit/s.

If Stream Pair Selection capability is enabled (see switching configuration section), this

pin is the ST-BUS stream 8 output.

When non-multiplexed bus structure is used, this pin should be connected to ground.

4