MT89L80AP Просмотр технического описания (PDF) - Mitel Networks

Номер в каталоге

Компоненты Описание

производитель

MT89L80AP Datasheet PDF : 15 Pages

| |||

MT89L80

Advance Information

STi3

7

STi4

8

STi5

9

STi6 10

STi7

11

VDD

12

F0i 13

C4i 14

A0

15

A1

16

A2

17

39 STo3

38 STo4

37 STo5

36 STo6

35 STo7

34 VSS

33 D0

32 D1

31 D2

30 D3

29 D4

44 PIN PLCC

VSS

1

DTA 2

STi0 3

STi1 4

STi2 5

NC 6

STi3 7

STi4 8

STi5 9

STi6 10

STi7 11

VDD 12

RESET 13

F0i 14

C4i 15

A0 16

A1 17

A2 18

NC 19

A3 20

A4 21

A5 22

DS 23

R/W 24

48 CSTo

47 ODE

46 STo0

45 STo1

44 STo2

43 NC

42 STo3

41 STo4

40 STo5

39 STo6

38 STo7

37 VSS

36 VDD

35 D0

34 D1

33 D2

32 D3

31 D4

30 NC

29 D5

28 D6

27 D7

26 CS

25 VSS

48 PIN SSOP

(JEDEC MO-118, 300mil Wide)

Pin Description

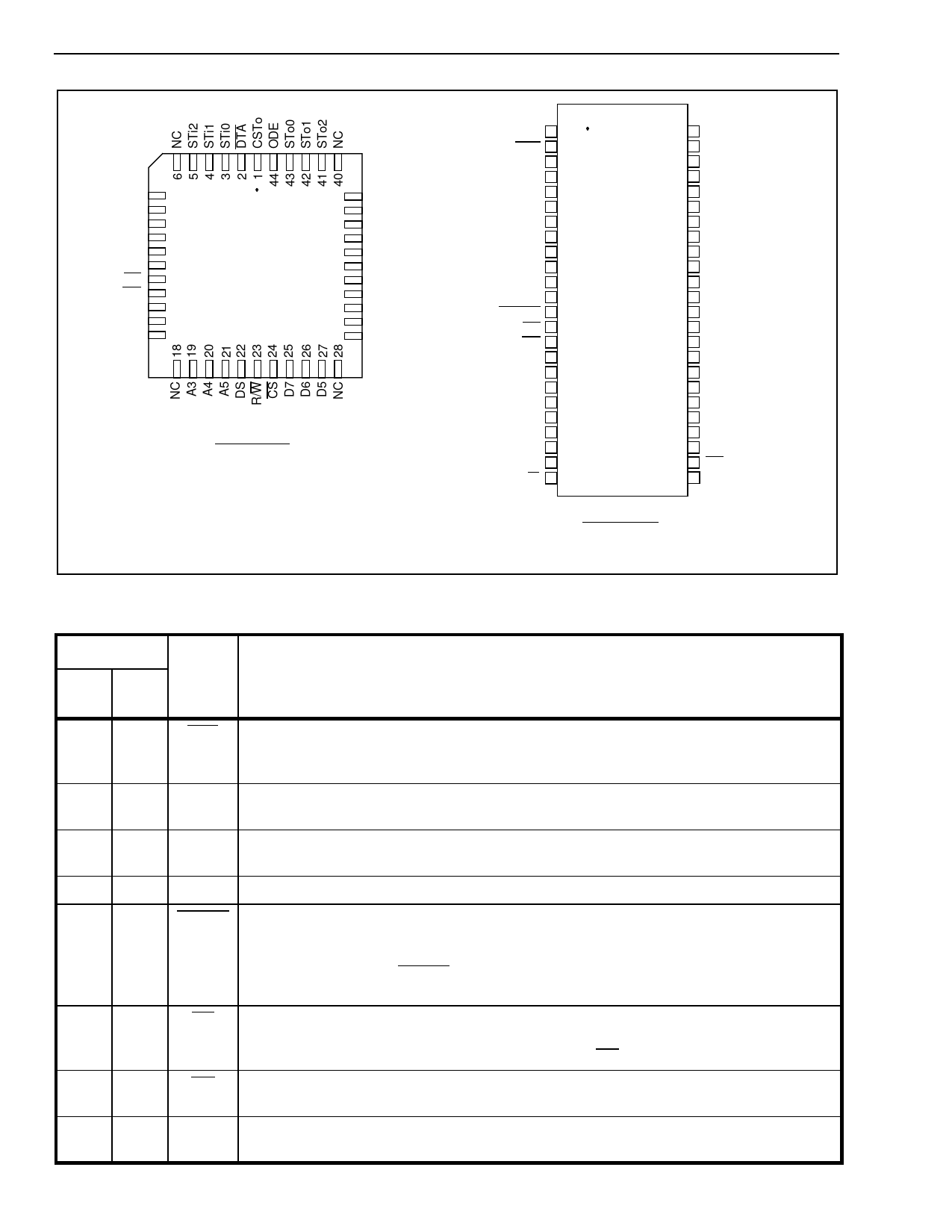

Figure 2 - Pin Connections

Pin #

44 48

PLCC SSOP

Name

Description

2

2

DTA Data Acknowledgment (5V Tolerant Three-state Output). This active low output

indicates that a data bus transfer is complete. A pull-up resistor is required at this

output.

3-5

7-11

12

13

14

3-5 STi0-2 ST-BUS Inputs 0 to 2 (5V-tolerant Inputs). Serial data input streams. These streams

have data rates of 2.048Mbit/s with 32 channels.

7-11 STi3-7 ST-BUS Inputs 3 to 7 (5V-tolerant Inputs). Serial data input streams. These streams

may have data rates of 2.048Mbit/s with 32channels.

12,36

13

VDD +3.3 Volt Power Supply.

RESET Device Reset ( 5v-tolerant input). This pin is only available for the 48-pin SSOP

package.This active low input puts the device in its reset state. It clears the internal

counters and registers. All ST-BUS outputs are set to the high impedance state. In

normal operation. The RESET pin must be held low for a minimum of 100nsec to reset

the device.

14

F0i Frame Pulse (5V-tolerant Input). This is the input for the frame synchronization

pulse for the 2048 kbit/s ST-BUS streams. A low on this input causes the internal

counter to reset on the next negative transition of C4i.

15

C4i 4.096 MHz Clock (5V-tolerant Input). ST-BUS bit cell boundaries lie on the alternate

falling edges of this clock.

15-17 16-18 A0-2 Address 0-2 / Input Streams 8-10 (5V-tolerant Input). These are the inputs for the

address lines on the microprocessor interface.

2-4