OR2C10A3S208I –Я—А–Њ—Б–Љ–Њ—В—А —В–µ—Е–љ–Є—З–µ—Б–Ї–Њ–≥–Њ –Њ–њ–Є—Б–∞–љ–Є—П (PDF) - Lattice Semiconductor

–Э–Њ–Љ–µ—А –≤ –Ї–∞—В–∞–ї–Њ–≥–µ

–Ъ–Њ–Љ–њ–Њ–љ–µ–љ—В—Л –Ю–њ–Є—Б–∞–љ–Є–µ

–њ—А–Њ–Є–Ј–≤–Њ–і–Є—В–µ–ї—М

OR2C10A3S208I Datasheet PDF : 192 Pages

| |||

Data Sheet

January 2002

ORCA Series 2 FPGAs

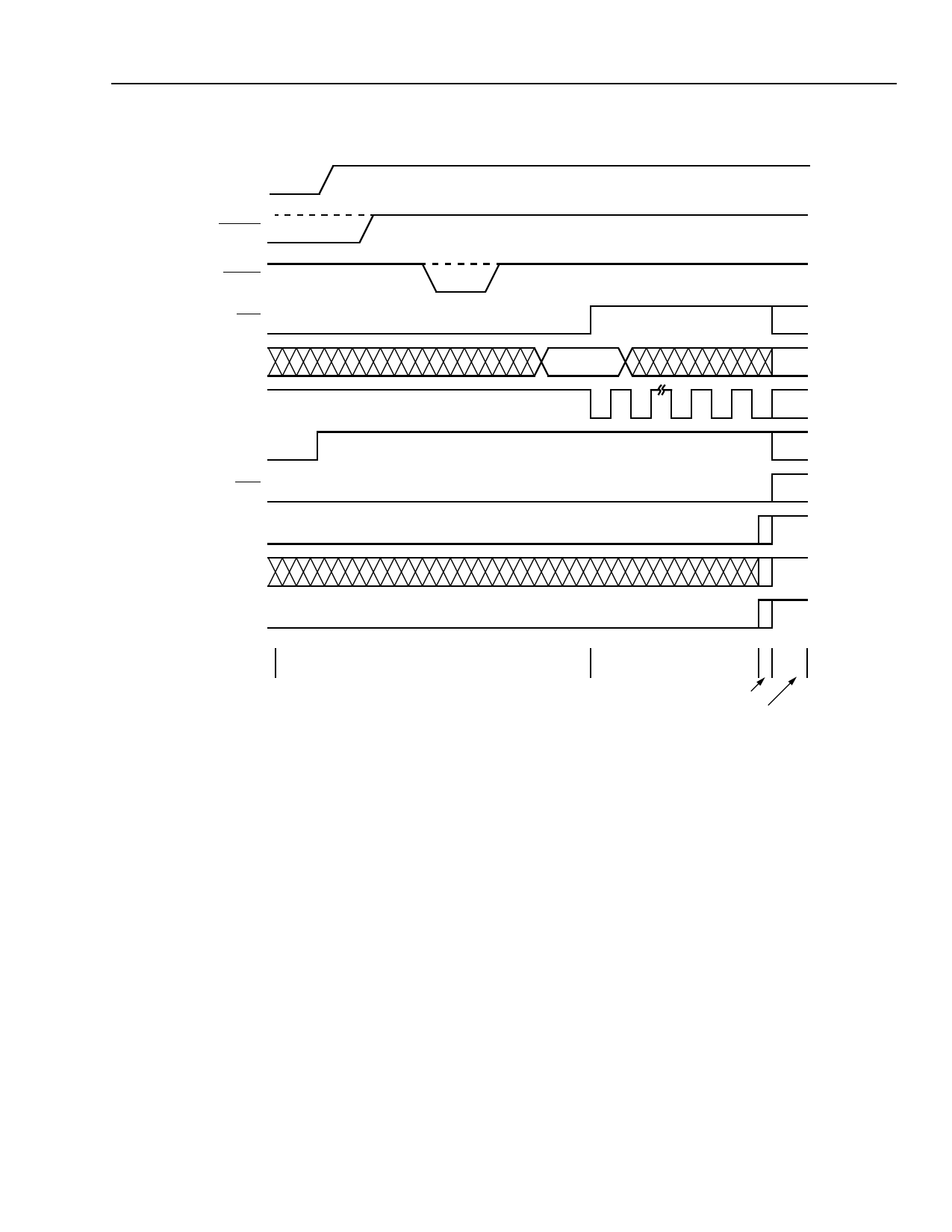

FPGA States of Operation (continued)

VDD

RESET

PRGM

INIT

M[3:0]

CCLK

HDC

LDC

DONE

USER I/O

INTERNAL

RESET

(gsm)

INITIALIZATION

CONFIGURATION

START-UP

OPERATION

Figure 37. Initialization/ConпђБguration/Start-Up Waveforms

5-4482(F)

All OR2CxxA I/Os operate as TTL inputs during conпђБg-

uration (OR2TxxA/OR2TxxB I/Os are CMOS-only). All

I/Os that are not used during the conпђБguration process

are 3-stated with internal pull-ups. During conпђБgura-

tion, the PLC latch/FFs are held set/reset and the inter-

nal BIDI buffers are 3-stated. The TRIDIs in the PICs

are not 3-stated. The combinatorial logic begins to

function as the FPGA is conпђБgured. Figure 37 shows

the general waveform of the initialization, conпђБguration,

and start-up states.

ConпђБguration

The ORCA Series FPGA functionality is determined by

the state of internal conпђБguration RAM. This conпђБgura-

tion RAM can be loaded in a number of different

modes. In these conпђБguration modes, the FPGA can

act as a master or a slave of other devices in the sys-

tem. The decision as to which conпђБguration mode to

use is a system design issue. The next section dis-

cusses conпђБguration in detail, including the conпђБgura-

tion data format and the conпђБguration modes used to

load the conпђБguration data in the FPGA.

Lattice Semiconductor

41