AD5721R Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

производитель

AD5721R Datasheet PDF : 36 Pages

| |||

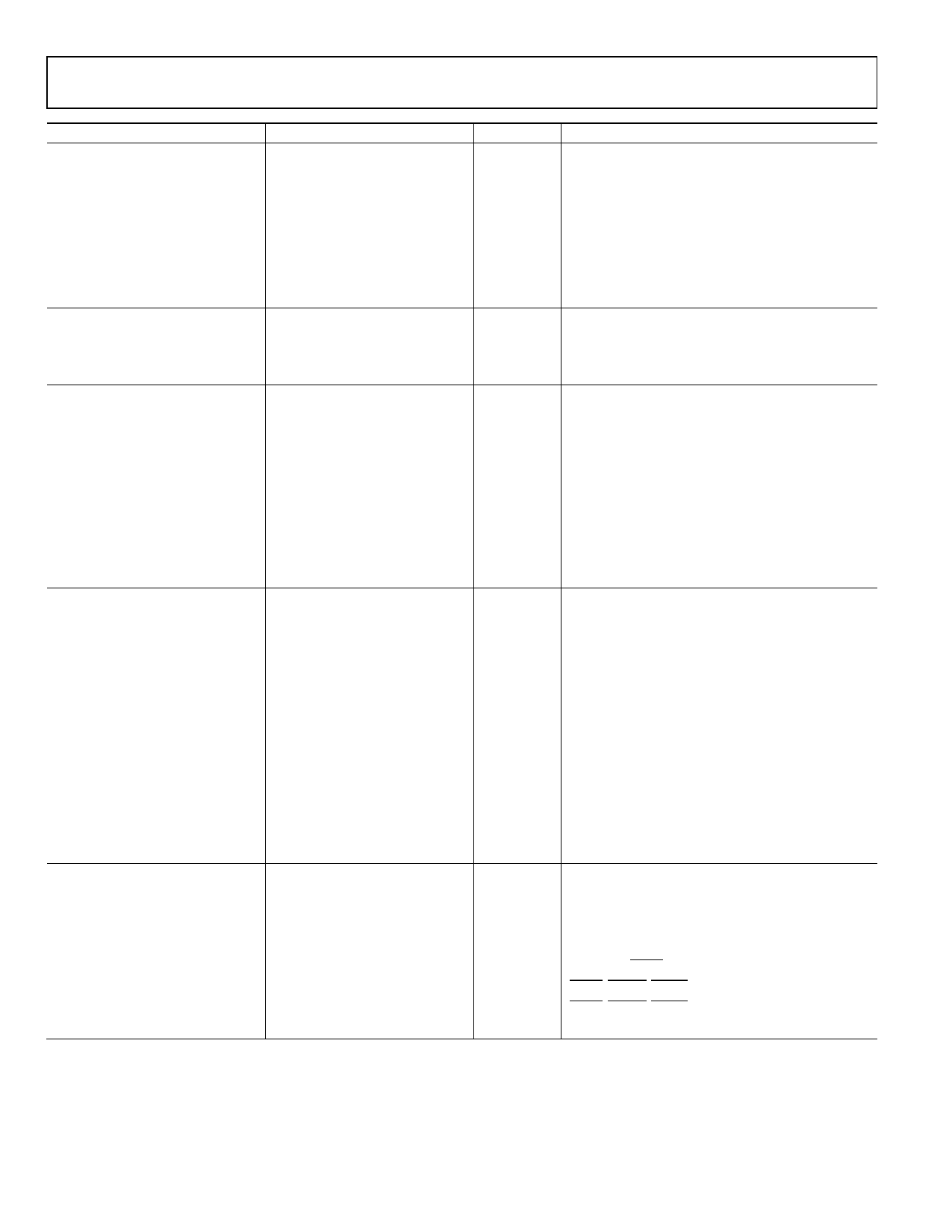

AD5761R/AD5721R

Data Sheet

Parameter2

Min

Typ Max

Unit

Test Conditions/Comments

Offset Error TC5

±5

µV/°C

Unipolar ranges, external reference3 and internal

reference

±15

µV/°C

Bipolar ranges, external reference3 and internal

reference

Gain Error

−0.1

+0.1

% FSR

External reference3

−0.15

+0.15

% FSR

Internal reference

Gain Error TC5

±1.5

ppm FSR/°C External reference3 and internal reference

TUE

−0.1

+0.1

% FSR

External reference3

−0.15

+0.15

% FSR

Internal reference

REFERENCE INPUT (EXTERNAL)5

Reference Input Voltage (VREF)

Input Current

−2

2.5

V

±0.5 +2

µA

±1% for specified performance

Reference Range

2

3

V

REFERENCE OUTPUT (INTERNAL)5

Output Voltage

2.5

V

±3 mV, at ambient temperature

Voltage Reference TC

2

5

ppm/°C

Output Impedance

25

kΩ

Output Voltage Noise

6

µV p-p

0.1 Hz to 10 Hz

Noise Spectral Density

10

nV/√Hz

At ambient; f = 10 kHz

Line Regulation

6

µV/V

At ambient

Thermal Hysteresis

80

ppm

First temperature cycle

Start-Up Time

3.5

ms

Coming out of power-down mode with a 10 nF

capacitor on the VREFIN/VREFOUT pin to improve noise

performance; outputs unloaded

OUTPUT CHARACTERISTICS5

Output Voltage Range

−VOUT

+VOUT

See Table 7 for the different output voltage ranges

available

−10

+10

V

VDD/VSS = ±11 V, ±10 V output range

−10.5

+10.5

V

VDD/VSS = ±11 V, ±10 V output range with 5%

overrange

Capacitive Load Stability

1

nF

Headroom

0.5 1

V

RLOAD = 1 kΩ for all ranges except 0 V to16 V and 0 V

to 20 V ranges (RLOAD = 2 kΩ)

Output Voltage TC

±3

ppm FSR/°C ±10 V range, external reference

Short-Circuit Current

25

mA

Short on the VOUT pin

Resistive Load

1

kΩ

All ranges except 0 V to16 V and 0 V to 20 V

2

kΩ

0 V to 16 V, 0 V to 20 V ranges

Load Regulation

0.3

mV/mA

Outputs unloaded

DC Output Impedance

0.5

Ω

Outputs unloaded

LOGIC INPUTS5

DVCC = 1.7 V to 5.5 V, JEDEC compliant

Input Voltage

High, VIH

0.7 × DVCC

V

Low, VIL

0.3 × DVCC V

Input Current

Leakage Current

−1

+1

µA

SDI, SCLK, SYNC

−1

+1

µA

LDAC, CLEAR, RESET pins held high

−55

µA

LDAC, CLEAR, RESET pins held low

Pin Capacitance

5

pF

Per pin, outputs unloaded

Rev. C | Page 4 of 36