Z380 Просмотр технического описания (PDF) - Zilog

Номер в каталоге

Компоненты Описание

производитель

Z380 Datasheet PDF : 115 Pages

| |||

ZILOG

EXTERNAL INTERFACE (Continued)

MICROPROCESSOR

IOCLK

1

2

3

4

5

6

7

8

9

10

ADDRESS

DATA

EDED

4D4D

/WAIT

/M1

/IORQ

/IORD

/IOWR

/INTAK

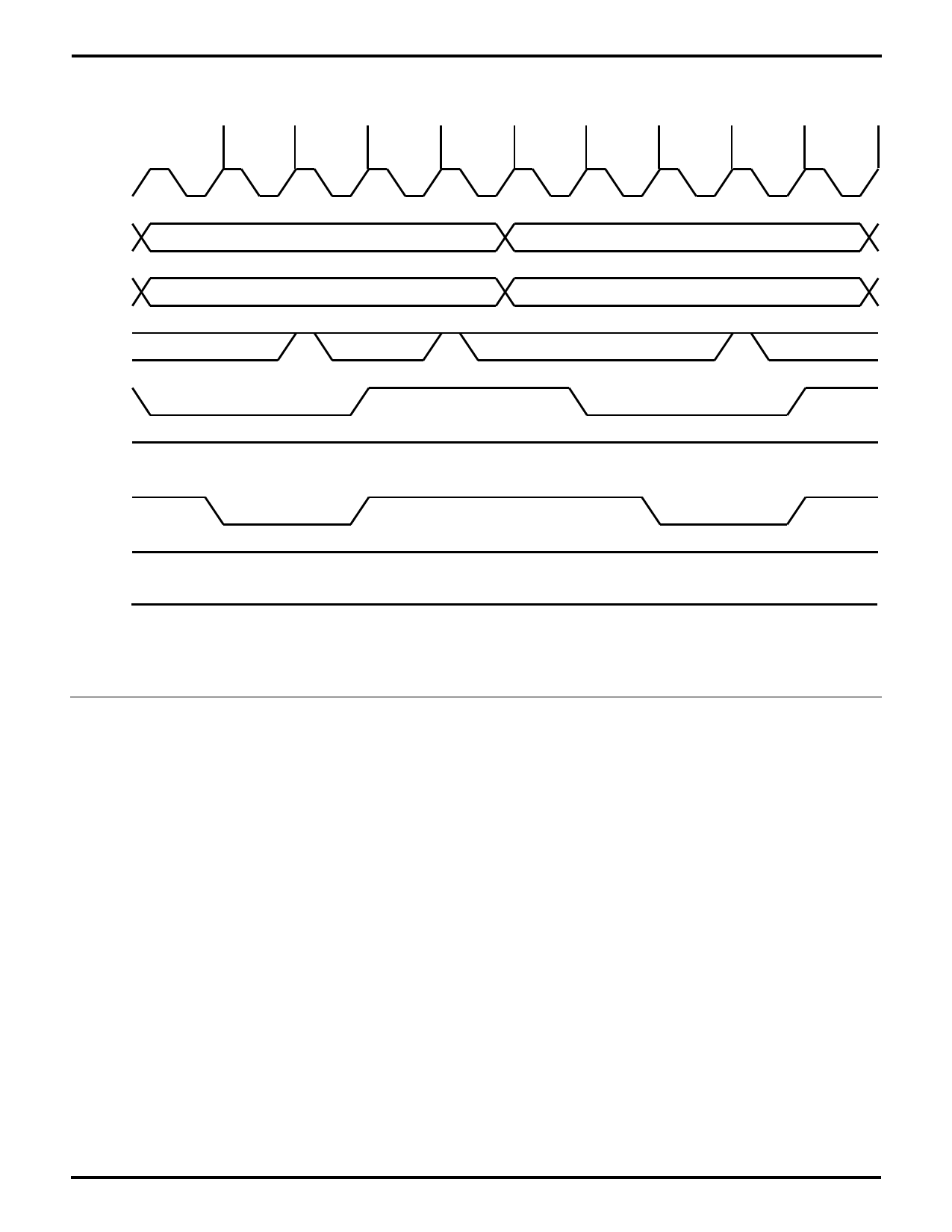

Figure 11. Return From Interrupt Cycle

The RETI transaction is ten IOCLK cycles long unless

extended by Wait states, and /WAIT is sampled at three

separate points during the transaction. /WAIT is first

sampled in the middle of the third IOCLK cycle to allow for

longer /IORD Low-time requirements. /WAIT is then sampled

again during the middle of the fifth IOCLK cycle to allow for

longer internal daisy-chain settling time within the periph-

eral. Wait states inserted here have the effect of separating

what the peripheral sees as two separate instruction fetch

cycles. Finally, /WAIT is sampled in the middle of the ninth

IOCLK cycle, again to allow for longer /IORD Low-time

requirements.

The Z380 MPU drives the data bus throughout the RETI

transaction, with EDEDH during the first half of the transac-

tion (the first byte of a RETI instruction is EDH) and with

4D4DH during the second half of the transaction (the

second byte of an RETI instruction is 4DH).

HALT Transactions

A HALT transaction occurs whenever the Z380 MPU ex-

ecutes a Halt instruction, with the /HALT signal activated

on the falling edge of BUSCLK. If the standby mode is not

enabled, executing a Sleep instruction would also cause a

Halt transaction to occur. While in the Halt state, the Z380

MPU continues to drive the address and data buses, and

the /HALT signal remains active until either an interrupt

request is acknowledged or a reset is received. Refresh

transactions may occur while in the halt state and the bus

can be granted. The timing of entry into the Halt state is

shown in Figure 12, while the timing of exiting from Halt

state is shown in Figure 13.

PS010001-0301