Z380 Просмотр технического описания (PDF) - Zilog

Номер в каталоге

Компоненты Описание

производитель

Z380 Datasheet PDF : 115 Pages

| |||

ZILOG

EXTERNAL INTERFACE (Continued)

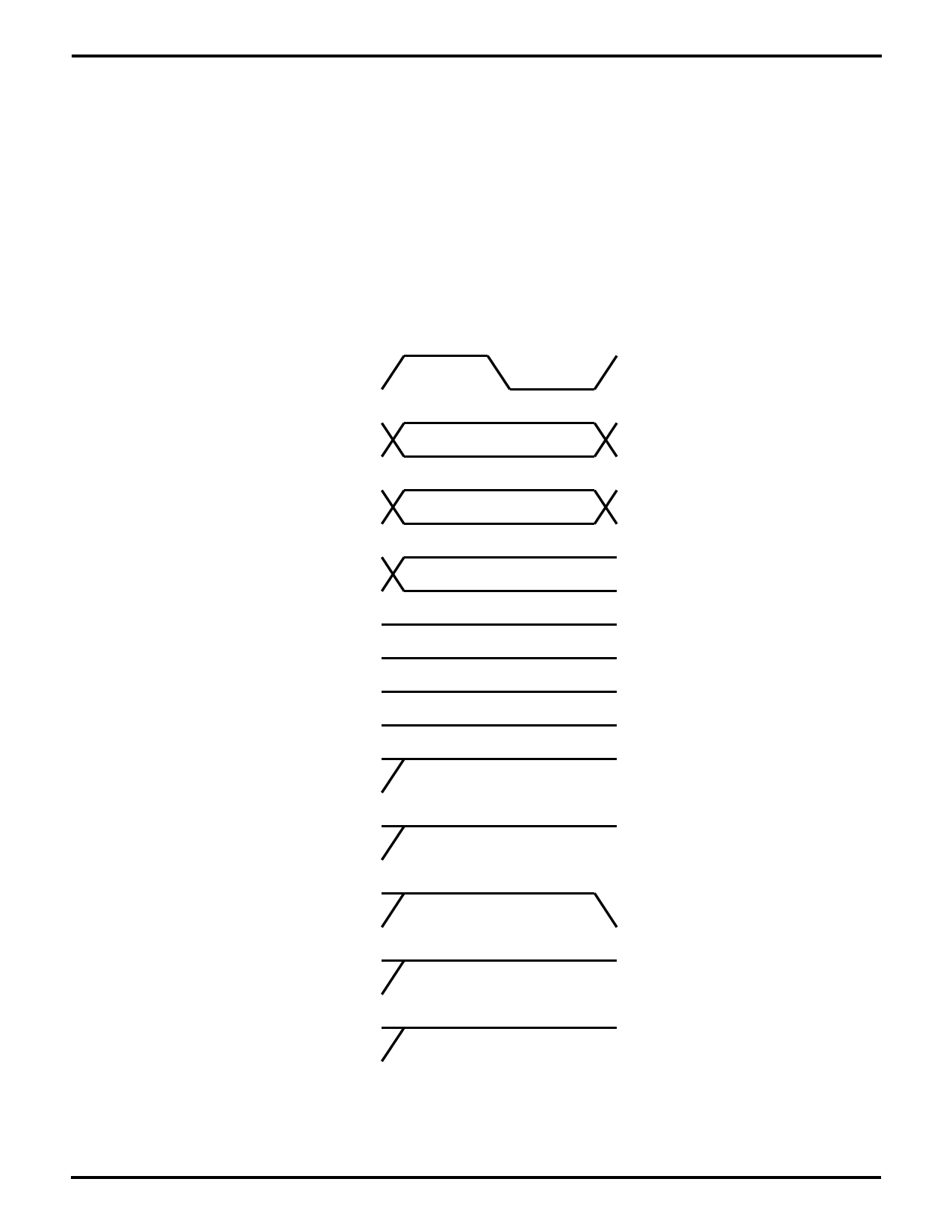

Refresh Transactions

A memory refresh transaction is generated by the Z380

MPU refresh controller and can occur immediately after

the final clock cycle of any other transaction. The address

during the refresh transaction is not defined as the

CAS-before-RAS refresh cycle is assumed, which uses the

on-chip refresh address generator present on DRAMs.

Prior to the first refresh transaction, a refresh setup cycle

is performed to guarantee that the /CAS precharge time is

met. This refresh setup cycle is present only prior to the first

MICROPROCESSOR

refresh transaction in a burst (Figure 5). Refresh transac-

tions are shown without wait states, with wait states be-

tween T1 and T2, between T2 and T3, and between T3 and

T4 (Figures 6A-D). Note that during the refresh cycle the

data bus is continuously driven, /MRD and /MWR remain

inactive, /BHEN and /BLEN are active to enable all /CAS

signals to the DRAMS, and those Chip Select signals

enabled for DRAM refresh transactions are active.

TPH

TPL

BUSCLK

ADDRESS

DATA

STATUS

/WAIT

/MSIZE

/TREFR

/TREFA

/TREFC

/MRD

/MWR

Figure 5. Refresh Setup

PS010001-0301