ADV101KP80 Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

производитель

ADV101KP80 Datasheet PDF : 12 Pages

| |||

ADV101

TIMING CHARACTERISTICS1

(VAA = +5 V ؎ 5%; VREF = +1.235 V; RL = 37.5 ⍀, CL = 10 pF; RSET = 560 ⍀.

ISYNC connected to IOG. All Specifications TMIN to TMAX2 unless otherwise noted.)

Parameter 80 MHz Version 50 MHz Version 30 MHz Version Units

Conditions/Comments

fMAX

80

50

t1

3

6

t2

2

2

t3

12.5

20

t4

4

7

t5

4

7

t6

30

30

20

20

t7

3

3

t83

12

15

30

MHz max Clock Rate

8

ns min

Data & Control Setup Time

2

ns min

Data & Control Hold Time

33.3

ns min

Clock Cycle Time

9

ns min

Clock Pulse Width High Time

9

ns min

Clock Pulse Width Low Time

30

ns max

Analog Output Delay

20

ns typ

3

ns max

Analog Output Rise/Fall Time

15

ns typ

Analog Output Transition Time

NOTES

1TTL input values are 0 to 3 volts, with input rise/fall times ≤3 ns, measured between the 10% and 90% points. Timing reference points at 50% for inputs and out-

puts. See timing notes in Figure 1.

2Temperature range (TMIN to TMAX): 0°C to +70°C.

3Sample tested at +25°C to ensure compliance.

Specifications subject to change without notice.

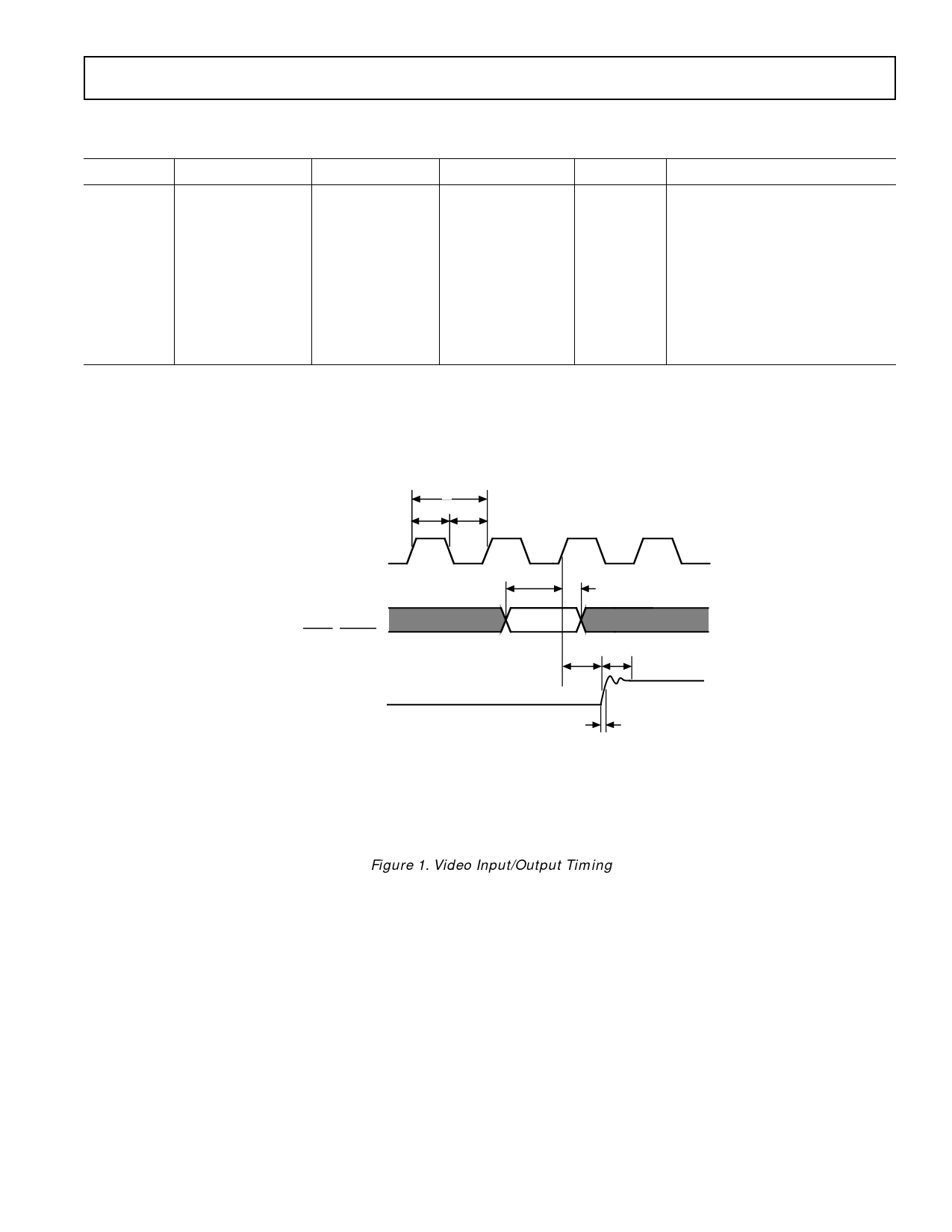

t3

t4

t5

CLOCK

DIGITAL INPUTS

(R0–R7, G0–G7, B0–B7;

SYNC, BLANK,

REF WHITE)

t1

t2

DATA

t6 t8

ANALOG OUTPUTS

(IOR, IOG, IOB, I SYNC)

t7

NOTES

1. OUTPUT DELAY (t6) MEASURED FROM THE 50% POINT OF THE RISING EDGE OF

CLOCK TO THE 50% POINT OF FULL-SCALE TRANSITION.

2. TRANSITION TIME ( t8) MEASURED FROM THE 50% POINT OF FULL-SCALE

TRANSITION TO WITHIN 2% OF THE FINAL OUTPUT VALUE.

3. OUTPUT RISE/FALL TIME ( t7) MEASURED BETWEEN THE 10% AND 90% POINTS

OF FULL TRANSITION.

Figure 1. Video Input/Output Timing

REV. B

–3–