MPC7457(2004) Просмотр технического описания (PDF) - Freescale Semiconductor

Номер в каталоге

Компоненты Описание

производитель

MPC7457 Datasheet PDF : 68 Pages

| |||

Electrical and Thermal Characteristics

5.2.3 L3 Clock AC Specifications

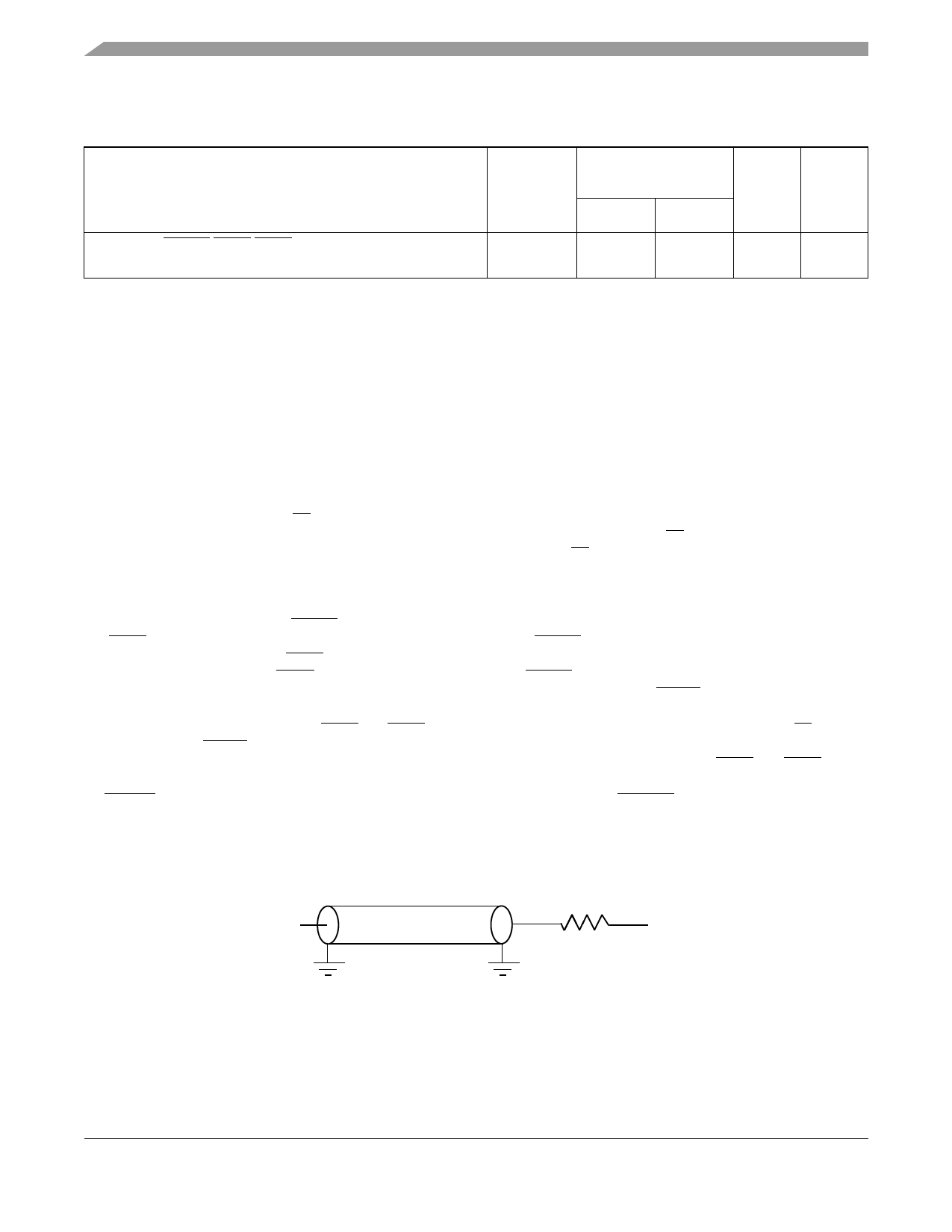

The L3_CLK frequency is programmed by the L3 configuration register core-to-L3 divisor ratio. See Table 18 for

example core and L3 frequencies at various divisors. Table 10 provides the potential range of L3_CLK output AC

timing specifications as defined in Figure 7.

The maximum L3_CLK frequency is the core frequency divided by two. Given the high core frequencies available

in the MPC7457, however, most SRAM designs will be not be able to operate in this mode using current technology

and, as a result, will select a greater core-to-L3 divisor to provide a longer L3_CLK period for read and write access

to the L3 SRAMs. Therefore, the typical L3_CLK frequency shown in Table 10 is considered to be the practical

maximum in a typical system. The maximum L3_CLK frequency for any application of the MPC7457 will be a

function of the AC timings of the MPC7457, the AC timings for the SRAM, bus loading, and printed-circuit board

trace length, and may be greater or less than the value given in Table 10. Note that SYSCLK input jitter and

L3_CLK[0:1] output jitter are already comprehended in the L3 bus AC timing specifications and do not need to be

separately accounted for in an L3 AC timing analysis. Clock skews, where applicable, do need to be accounted for

in an AC timing analysis.

Freescale is similarly limited by system constraints and cannot perform tests of the L3 interface on a socketed part

on a functional tester at the maximum frequencies of Table 10. Therefore, functional operation and AC timing

information are tested at core-to-L3 divisors which result in L3 frequencies at 250 MHz or lower.

Table 10. L3_CLK Output AC Timing Specifications

At recommended operating conditions. See Table 4.

Device Revision (L3 I/O Voltage) 6

Parameter

Symbol

Rev 1.1. (All I/O Modes)

Rev 1.2

Rev 1.2 (1.5-V I/O Mode) (1.8-, 2.5-V I/O Modes)

Unit Notes

L3 clock frequency

L3 clock cycle time

L3 clock duty cycle

L3 clock output-to-output skew

(L3_CLK0 to L3_CLK1)

L3 clock output-to-output skew

(L3_CLK[0:1] to

L3_ECHO_CLK[1,3])

Min Typ Max Min Typ Max

fL3_CLK

—

200

—

—

250

—

MHz

1

tL3_CLK

—

5.0

—

—

4.0

—

ns

1

tCHCL/tL3_CLK

—

50

—

—

50

—

%

2

tL3CSKW1

—

—

100

—

—

100

ps

3

tL3CSKW2

—

—

100

—

—

100

ps

4

MPC7457 RISC Microprocessor Hardware Specifications, Rev. 5

20

Freescale Semiconductor