MC6800P Просмотр технического описания (PDF) - Motorola => Freescale

Номер в каталоге

Компоненты Описание

производитель

MC6800P Datasheet PDF : 32 Pages

| |||

I

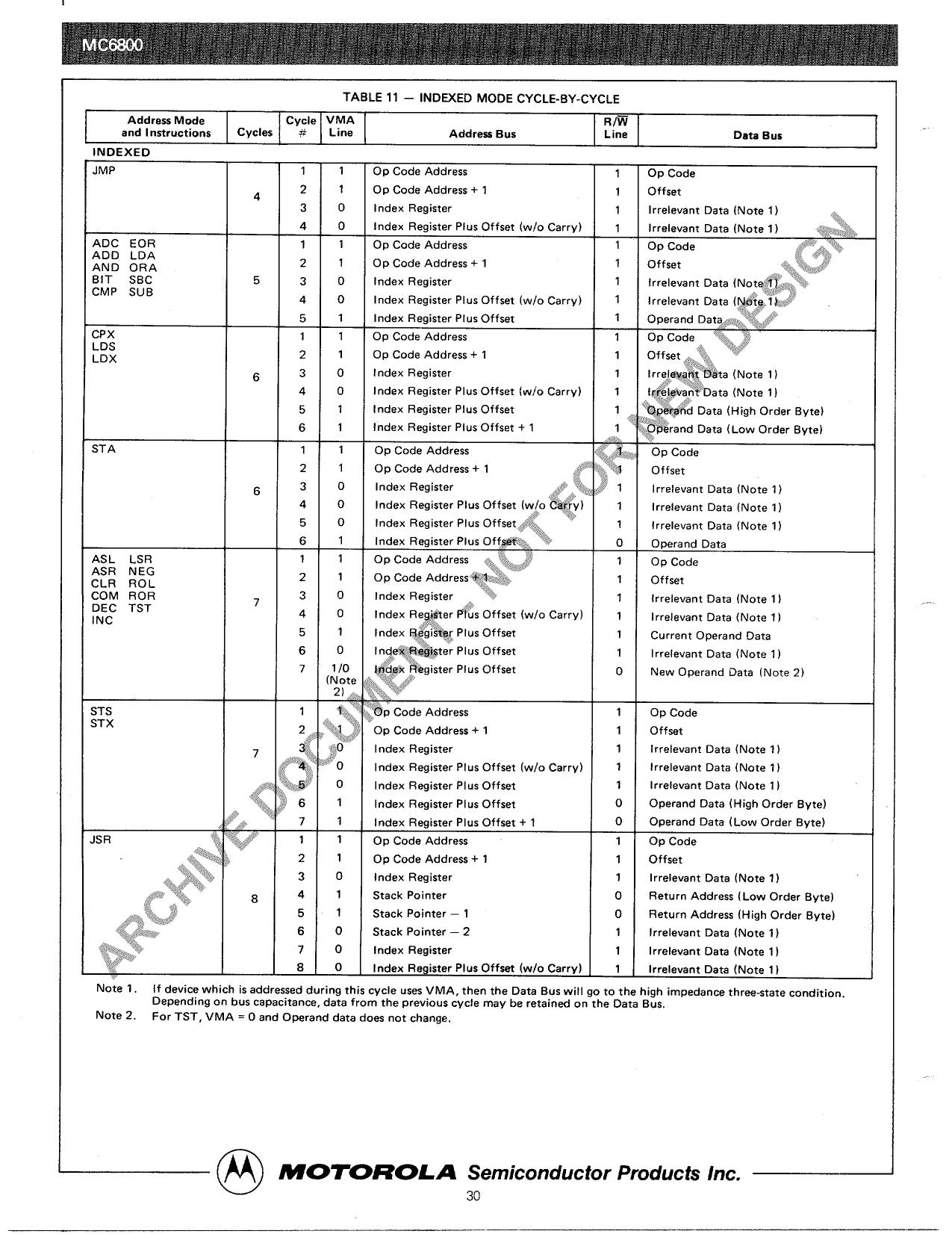

TABLE 11 – INDEXEO MOOE CYCLE-BY-CYCLE

Address Mode

and Instructions

INDEXED

JMP

Cycle VMA

Cycles

#

Line

Address Bus

T

1

Op Code Address

R 1~

Line

Deta Bus

I

2

1

OP Code Address + 1

4

3

0

Index Register

ADC

ADD

AND

BIT

CMP

EOR

LDA

ORA

SBC

SUB

4

0

TT

Index Register Plus Offset (w/o Carry)

Op Code Address

2

1

Op Code Address + 1

5

3

0

Index Register

4

0

Index Register PI us Offset (w/o Carry)

5

1

Index Register Plus Offset

CPX

LDS

LDX

1

2

6

3

4

Op Code Address

Op Code Address+ 1

Index Register

Index Register Plus Offset (w/o Carry)

lg{&,~@van#Data (Note 1)

STA

5

6

1

2

6

3

4

Index Register Plus Offset

Index Register Plus Offset + 1

Op Code Address

Op Code Address + 1

Index Register

Index Register Plus Offset

.7,,>,,.,,

,,+y:>,

B:#

,$<’.i”?.!,,

(w/o *~/Y)

~~y

Data (High Order Byte)

~~~$rand Data (Low Order Byte)

,’

Op Code

Offset

Irrelevant Data (Note 1 )

Irrelevant Data (Note 1 )

ASL

ASR

CLR

COM

DEC

INC

LSR

NEG

ROL

ROR

TST

5

6

1

2

?

3

4

5

Index Register Plus Offset ,,:~j,

‘k

$.\\$&h

Index Register Plus Off@F?:~

Op Code Address

kTi\$ $:~t

‘i:%,>:.,.>\{“,:~b-

Op Code Address’~~%?.?#~

~~~.,;,\

Index Register , ‘.:

Index ReQ,..&.,,e,,r, Pyus Offset (w/o Carry)

Index ~{gf$~~{ Plus Offset

Irrelevant Oata (Note 1 )

Operand Data

Op Code

Offset

Irrelevant Data (Note 1 )

Irrelevant Data (Note 1 )

Current Operand Data

6

I nd.-e~‘l..%~$~+,t~ter PI us Offset

Irrelevant Data (Note 1 )

7

t#.;d$,:*,>~.:R,!*gister Plus Offset

New Operand Data (Note 2)

?n. S,pt:“+f

yt{\,

?

;TS

T

‘&p Code Address

1

Op Code

3TX

2

Op Code Address+ 1

1 Offset

3$$

Index Register

1

Irrelevant Data (Note 1 )

‘q;

Index Register Plus Offset (w/o Carry)

1

Irrelevant Data (Note 1 )

;@p

Index Register Plus Offset

1

Irrelevant Data (Note 1 )

6

Index Register Plus Offset

0

Operand Data ( High Order Byte)

7

Index Resister Plus Offset + 1

0

Operand Data ( Low Order Byte)

T

Op Code Address

1 Op Code

2

Op Code Address+ 1

1 Offset

3

Index Register

4

Stack Pointer

5

Stack Pointer – 1

1

Irrelevant Data (Note 1 )

0

Return Address ( Low Order Byte)

0

Return Address (High Order Byte)

6

Stack Pointer – 2

1

Irrelevant Data (Note 1 )

7

Index Register

1

Irrelevant Data (Note 1 )

—8

Index Register Plus Offset (w/o Carry)

1

Irrelevant Oata (Note 1 )

Note 1.

Note 2.

If device which is addressed during this cycle uses VMA, then the Data Bus will go to the high impedance

Oepending on bus capacitance, data from the previous cycle may be retained on the Oata Bus.

For TST, VMA = O and Operand data does not change.

three-state

condition.

—

MOTOROLA

Semiconductor Products Inc.

@

30