CXD2931GA-9 Просмотр технического описания (PDF) - Sony Semiconductor

Номер в каталоге

Компоненты Описание

производитель

CXD2931GA-9 Datasheet PDF : 27 Pages

| |||

CXD2931R-9/GA-9

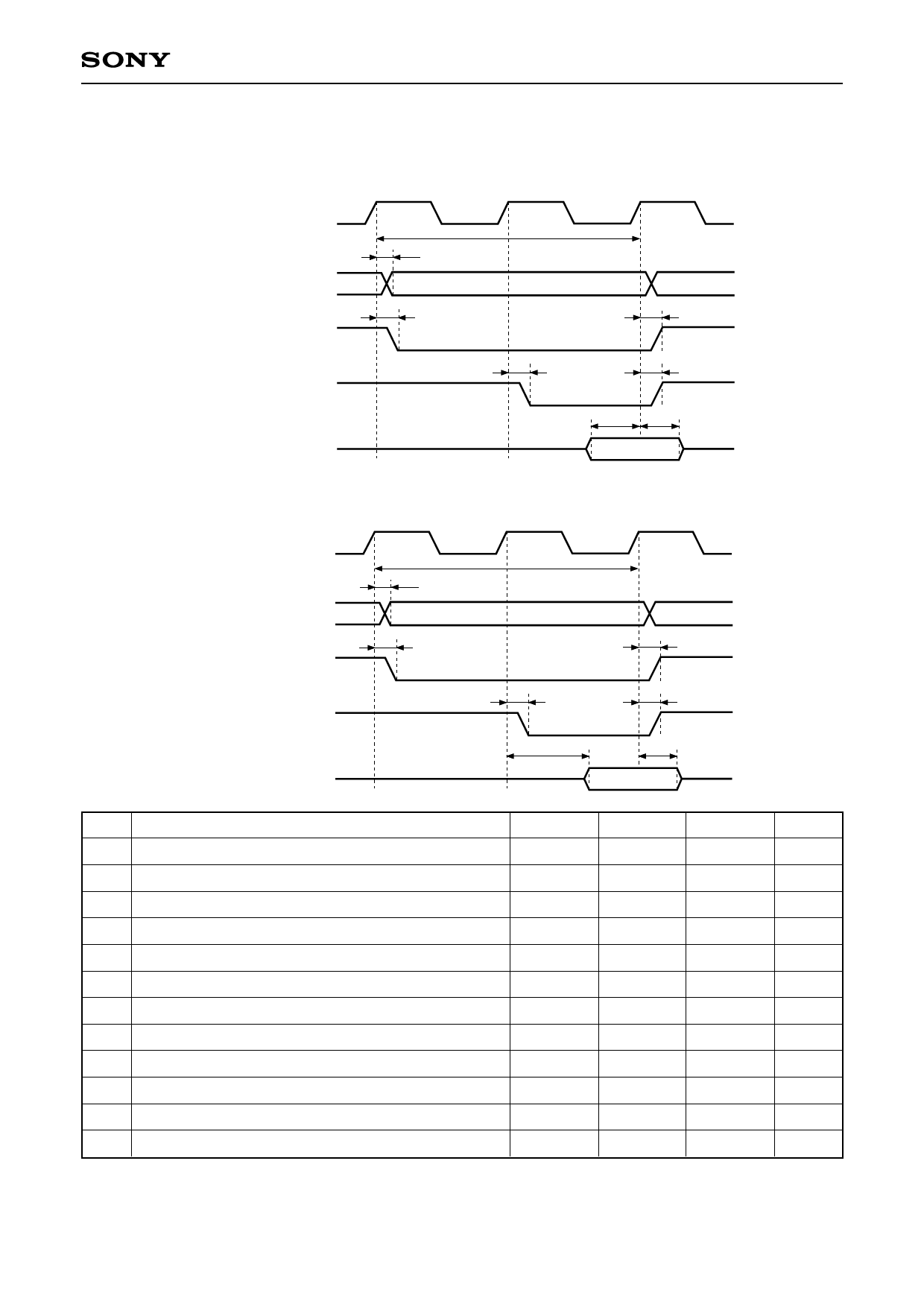

• External Data Access Timing (XCS0, DCS0 to DCS5/no data wait)

(1) Read (byte access/no data wait)

CLKOUT

(b)

DADR

(c)

XCS0, DCS0 to DCS5

DRD

DB

(a)

(d)

(e)

(f)

(g) (h)

(8)

(2) Write (byte access/no data wait)

CLKOUT

(b)

DADR

(c)

XCS0, DCS0 to DCS5

DWR

DB

(a)

(i)

(k)

No.

Item

Min.

(a) Read/write cycle time (Fex: @20MHz)

—

(b) Address delay time

—

(c) Chip select fall delay time

3

(d) Chip select rise delay time

3

(e) Read signal fall delay time

2

(f) Read signal rise delay time

2

(g) Read data setup time

16

(h) Read data hold time

0

(i) Write signal fall delay time

0

(j) Write signal rise delay time

0

(k) Write data established time

—

(l) Write data hold time

5

– 17 –

(d)

(j)

(l)

(8)

Typ.

Max.

Unit

100

—

ns

—

12

ns

—

13

ns

—

13

ns

—

8

ns

—

10

ns

—

—

ns

—

—

ns

—

2

ns

—

3

ns

—

12

ns

—

—

ns

∗ The load capacitance = 30pF.