AS3930 Просмотр технического описания (PDF) - austriamicrosystems AG

Номер в каталоге

Компоненты Описание

производитель

AS3930 Datasheet PDF : 32 Pages

| |||

AS3930

Datasheet - Detailed Description

Table 11. Bits B13-B8

B13

B12

B11

B10

B9

B8

0

0

1

0

1

1

0

0

1

1

0

0

0

0

1

1

0

1

Read/Write Register

R11

R12

R13

The last 8 bits are the data that has to be written respectively read. A CS toggle high-low-high terminates the command mode.

If a direct command is sent (B15-B14=11), then the bits from B13 to B8 define the direct command while the last 8 bits are omitted. Table 12

shows all possible direct commands.

Table 12. List of Direct Commands

COMMAND_MODE

B13

B12

B11

B10

B9

B8

clear_wake

0

0

0

0

0

0

reset_RSSI

0

0

0

0

0

1

trim_osc

0

0

0

0

1

0

clear_false

0

0

0

0

1

1

preset_default

0

0

0

1

0

0

All direct commands are explained below:

- clear_wake: Clears the wake state of the chip. In case the chip has woken up (WAKE pin is high), the chip is set back to listening mode.

- reset_RSSI: Resets the RSSI measurement.

- trim_osc: Starts the trimming procedure of the internal RC oscillator (see Figure 20).

- clear_false: Resets the false wake-up register (R13<7:0>=00).

- preset_default: Sets all registers in the default mode, as shown in Figure 7.

Note: In order to get the AS3930 work properly after sending the preset_default direct command, it is mandatory to write R0<3>=0 and

R0<2>=0.

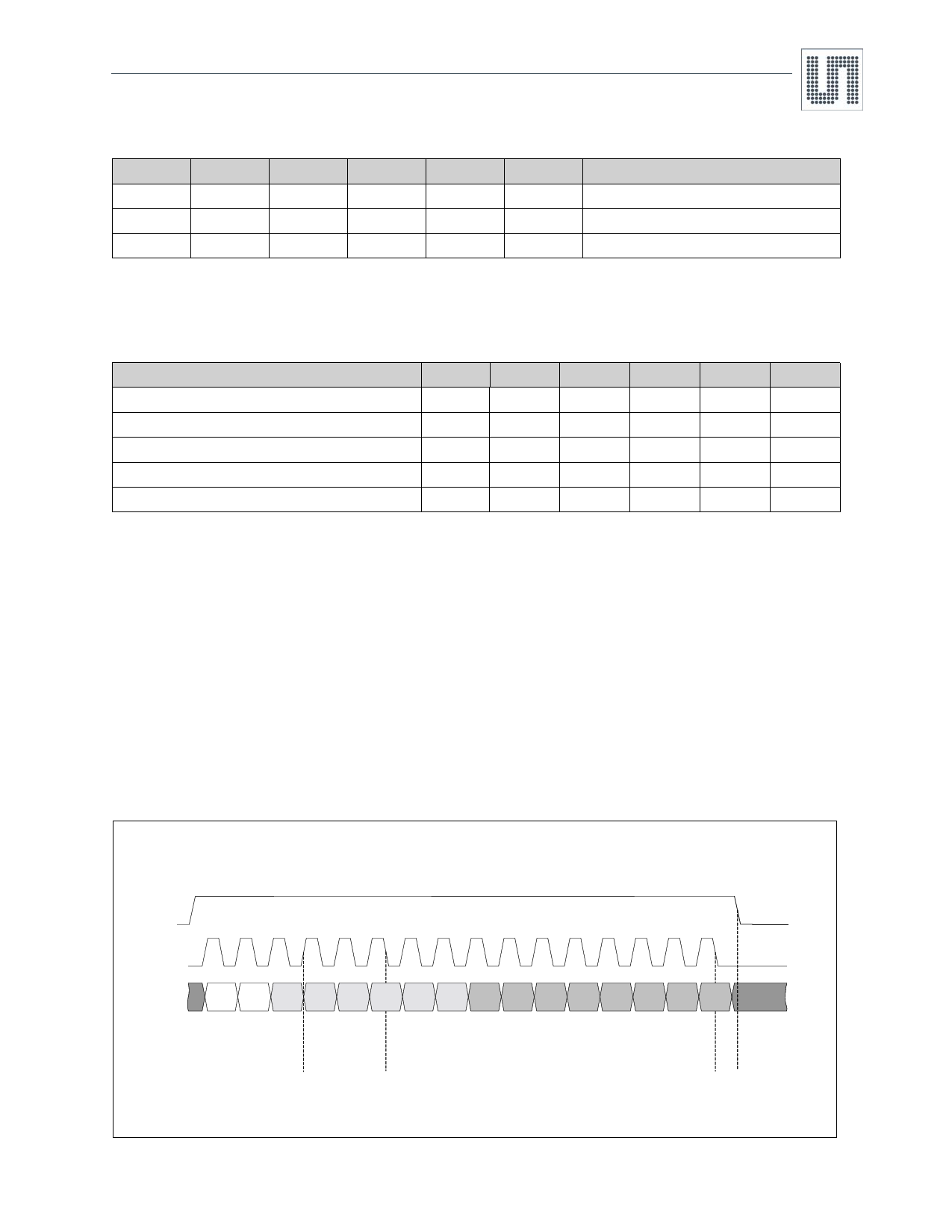

Writing of Data to Addressable Registers (WRITE Mode)

The SDI is sampled at the falling edge of SCLK (as shown in the following diagrams).

A CS toggling high-low-high indicates the end of the WRITE command after register has been written. The following example shows a write

command.

Figure 12. Writing of a Single Byte (falling edge sampling)

CS

SCLK

SDI X 0 0 A5 A4 A3 A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0

X

Two leading

Zeros indicate

WRITE Mode

SCLK rising

edge Data is

transfered from

µC

SCLK

falling edge

Data is

sampled

Data is moved

to Address

A5-A0

CS falling

edge signals

end of

WRITE Mode

www.ams.com/LF-Receiver/AS3930

Revision 1.5

15 - 32