ADSP-21261 Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

производитель

ADSP-21261 Datasheet PDF : 48 Pages

| |||

ADSP-21261/ADSP-21262/ADSP-21266

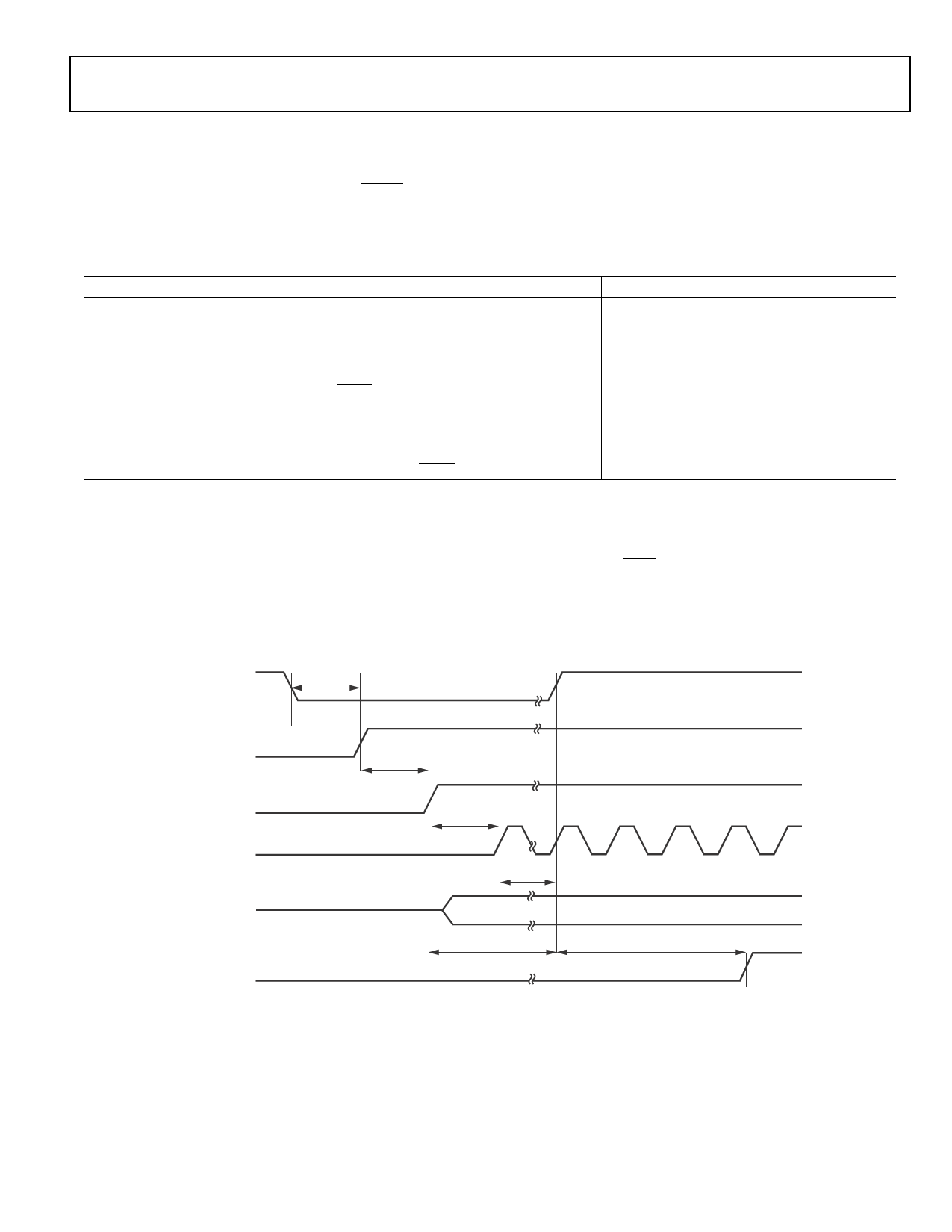

Power-Up Sequencing

The timing requirements for DSP startup are given in Table 15

and Figure 5. Note that during power-up, a leakage current of

approximately 200 A may be observed on the RESET pin. This

leakage current results from the weak internal pull-up resistor

on this pin being enabled during power-up.

Table 15. Power-Up Sequencing (DSP Startup)

Parameter

Min

Timing Requirements

tRSTVDD

RESET Low Before VDDINT/VDDEXT On

0

tIVDDEVDD

VDDINT On Before VDDEXT

–50

tCLKVDD

CLKIN Valid After VDDINT/VDDEXT Valid1

0

tCLKRST

CLKIN Valid Before RESET Deasserted

102

tPLLRST

PLL Control Setup Before RESET Deasserted

203

Max

Unit

ns

+200

ms

200

ms

μs

μs

Switching Characteristics

tCORERST

DSP Core Reset Deasserted After RESET Deasserted

4096 tCK4, 5

1 Valid VDDINT/VDDEXT assumes that the supplies are fully ramped to their 1.2 V and 3.3 V rails. Voltage ramp rates can vary from microseconds to hundreds of milliseconds

depending on the design of the power supply subsystem.

2 Assumes a stable CLKIN signal, after meeting worst-case startup timing of crystal oscillators. Refer to the crystal oscillator manufacturer’s data sheet for startup time. Assume

a 25 ms maximum oscillator startup time if using the XTAL pin and internal oscillator circuit in conjunction with an external crystal.

3 Based on CLKIN cycles.

4 Applies after the power-up sequence is complete. Subsequent resets require a minimum of four CLKIN cycles for RESET to be held low in order to properly initialize and

propagate default states at all I/O pins.

5 The 4096 cycle count depends on tSRST specification in Table 17. If setup time is not met, one additional CLKIN cycle can be added to the core reset time, resulting in 4097

cycles maximum.

RESET

tRSTVDD

VDDINT

VDDEXT

CLKIN

CLK_CFG1–0

RESETOUT

(MUXED WITH CLKOUT)

tIVDDEVDD

tCLKVDD

tCLKRST

tPLLRST

Figure 5. Power-Up Sequencing

tCORERST

Rev. G | Page 17 of 48 | December 2012