ADM1487EARZ(Rev0) –Я—А–Њ—Б–Љ–Њ—В—А —В–µ—Е–љ–Є—З–µ—Б–Ї–Њ–≥–Њ –Њ–њ–Є—Б–∞–љ–Є—П (PDF) - Analog Devices

–Э–Њ–Љ–µ—А –≤ –Ї–∞—В–∞–ї–Њ–≥–µ

–Ъ–Њ–Љ–њ–Њ–љ–µ–љ—В—Л –Ю–њ–Є—Б–∞–љ–Є–µ

–њ—А–Њ–Є–Ј–≤–Њ–і–Є—В–µ–ї—М

ADM1487EARZ

(Rev.:Rev0)

(Rev.:Rev0)

ADM1487EARZ Datasheet PDF : 16 Pages

| |||

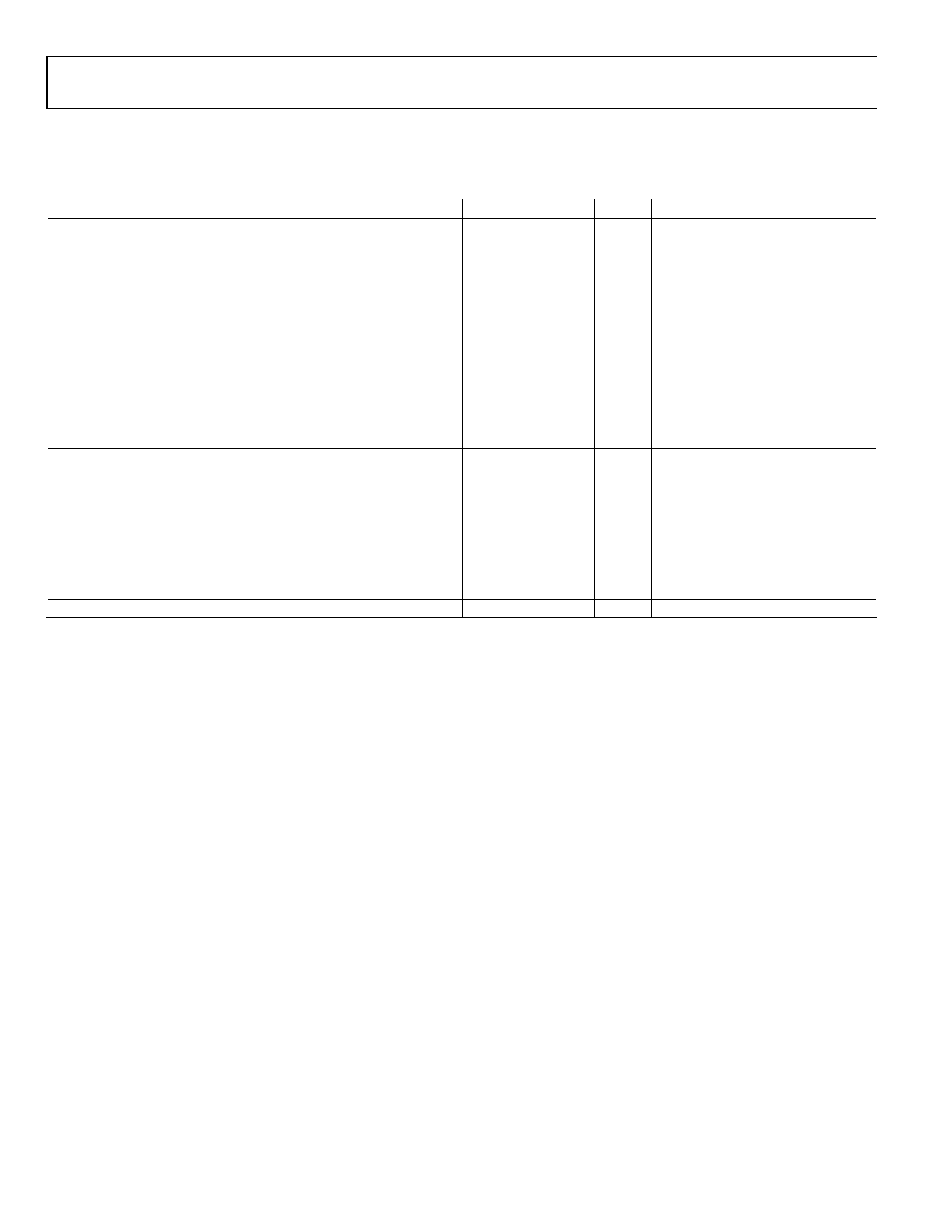

ADM485E/ADM487E/ADM1487E

TIMING SPECIFICATIONS

VCC = 5 V ± 5%, TA = TMIN to TMAX, unless otherwise noted.

Table 3. ADM485E/ADM1487E

Parameter

DRIVER

Input to Output

Output Skew to Output

Rise/Fall Time

Enable Time to High Level

Enable Time to Low Level

Disable Time from Low Level

Disable Time from High Level

RECEIVER

Input to Output

|tPLH вИТ tPHL| Differential Receiver Skew

Enable Time to Low Level

Enable Time to High Level

Disable Time from Low Level

Disable Time from High Level

MAXIMUM DATA RATE

Symbol Min Typ Max Unit Test Conditions/Comments

tDPLH

10 40 60

ns

RDIFF = 54 ќ©, CL1 = CL2 = 100 pF

(see Figure 19 and Figure 20)

tDPHL

10 40 60

ns

RDIFF = 54 ќ©, CL1 = CL2 = 100 pF

(see Figure 19 and Figure 20)

tSKEW

5

10

ns

RDIFF = 54 ќ©, CL1 = CL2 = 100 pF

(see Figure 19 and Figure 20)

tDR, tDF

3

20 40

ns

RDIFF = 54 ќ©, CL1 = CL2 = 100 pF

(see Figure 19 and Figure 20)

tDZH

45 70 ns CRL = 100 pF, S2 closed (see Figure 21)

tDZL

45 70 ns CRL = 100 pF, S1 closed (see Figure 22)

tDLZ

45 70 ns CRL = 15 pF, S1 closed (see Figure 22)

tDHZ

45 70 ns CRL = 15 pF, S2 closed (see Figure 21)

tRPLH

20 60 200 ns

RDIFF = 54 ќ©, CL1 = CL2 = 100 pF

(see Figure 23 and Figure 24)

tSKEW

5

ns

RDIFF = 54 ќ©, CL1 = CL2 = 100 pF

(see Figure 4 and Figure 5)

tRZL

25 50 ns CRL = 15 pF, S2 closed (see Figure 25)

tRZL

20 50 ns CRL = 15 pF, S1 closed (see Figure 25)

tRLZ

20 50 ns CRL = 15 pF, S2 closed (see Figure 25)

tRHZ

20 50

ns

tPLH, tPHL < 50% of data period

fMAX

2.5

Mbps

Rev. 0 | Page 4 of 16