CY7C68001(2004) Просмотр технического описания (PDF) - Cypress Semiconductor

Номер в каталоге

Компоненты Описание

производитель

CY7C68001 Datasheet PDF : 42 Pages

| |||

FO R

FO R

CY7C68001

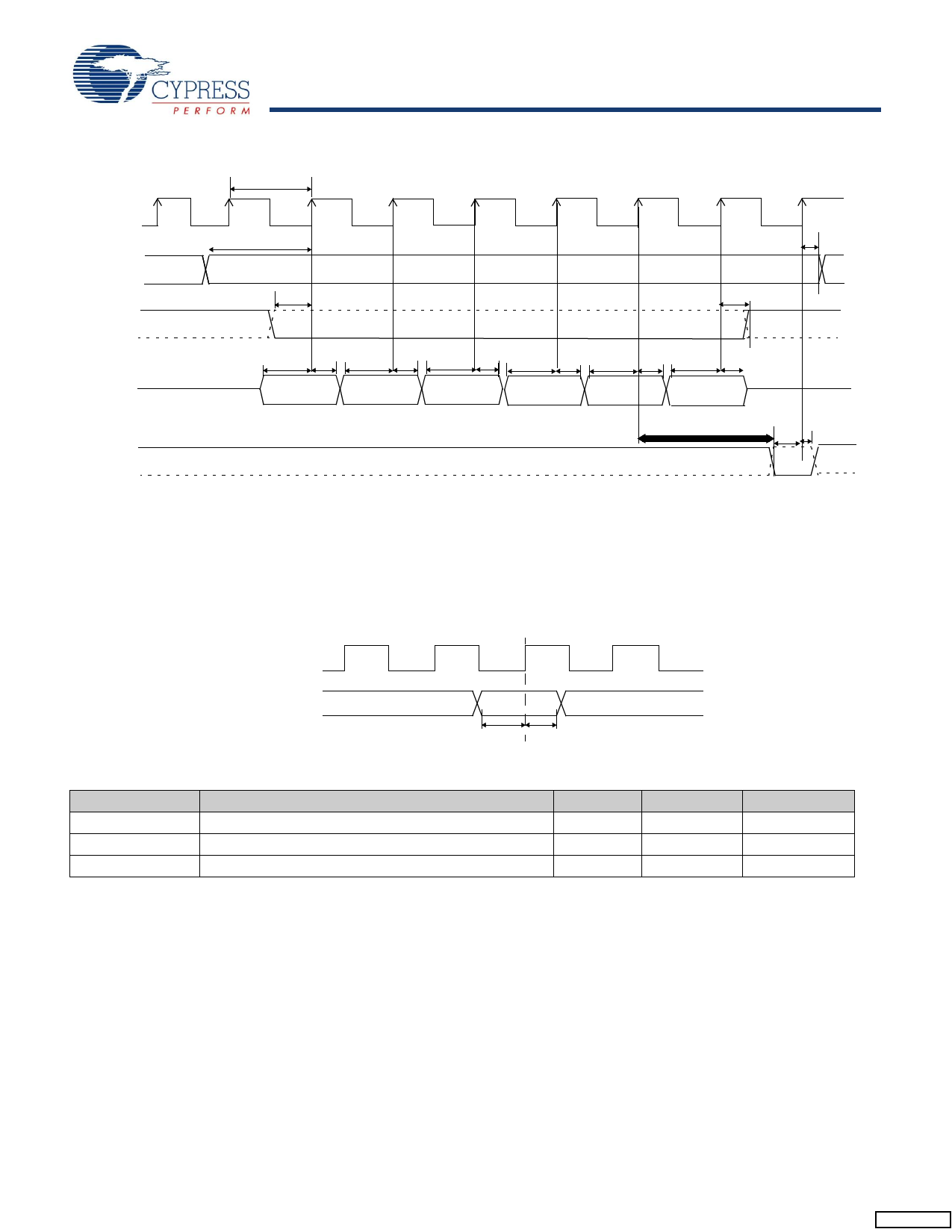

11.3.7 Slave FIFO Asynchronous Packet End Strobe

PKTEND

tPEpwl

tPEpwh

FLAGS

tXFLG

Figure 11-11. Slave FIFO Asynchronous Packet End Strobe Timing Diagram

Table 11-16. Slave FIFO Asynchronous Packet End Strobe Parameters[14]

Parameter

tPEpwl

tPWpwh

tXFLG

Description

PKTEND Pulse Width LOW

PKTEND Pulse Width HIGH

PKTEND to FLAGS Output Propagation Delay

Min.

50

50

Max.

110

11.3.8 Slave FIFO Asynchronous Address

SLCS/FIFOADR[2:0]

SLRD/SLWR/PKTEND

tSFA

tFAH

Figure 11-12. Slave FIFO Asynchronous Address Timing Diagram[12]

Table 11-17. Slave FIFO Asynchronous Address Parameters[14]

Parameter

tSFA

tFAH

tFAH

Description

FIFOADR[2:0] to RD/WR/PKTEND Set-up Time

SLRD/PKTEND to FIFOADR[2:0] Hold Time

SLWR to FIFOADR[2:0] Hold Time

Min.

10

20

70

Max.

11.4 Slave FIFO Address to Flags/Data

Following timing is applicable to synchronous and asynchronous interfaces.

FIFOADR [2.0]

FLAGS

tXFLG

tXFD

DATA

N

N+1

Figure 11-13. Slave FIFO Address to Flags/Data Timing Diagram[11]

Table 11-18. Slave FIFO Address to Flags/Data Parameters

Parameter

tXFLG

tXFD

Description

FIFOADR[2:0] to FLAGS Output Propagation Delay

FIFOADR[2:0] to FIFODATA Output Propagation Delay

Min.

Max.

10.7

14.3

Unit

ns

ns

ns

Unit

ns

ns

ns

Unit

ns

ns

Document #: 38-08013 Rev. *E

Page 30 of 42