CY7C68001(2004) Просмотр технического описания (PDF) - Cypress Semiconductor

Номер в каталоге

Компоненты Описание

производитель

CY7C68001 Datasheet PDF : 42 Pages

| |||

FO R

FO R

CY7C68001

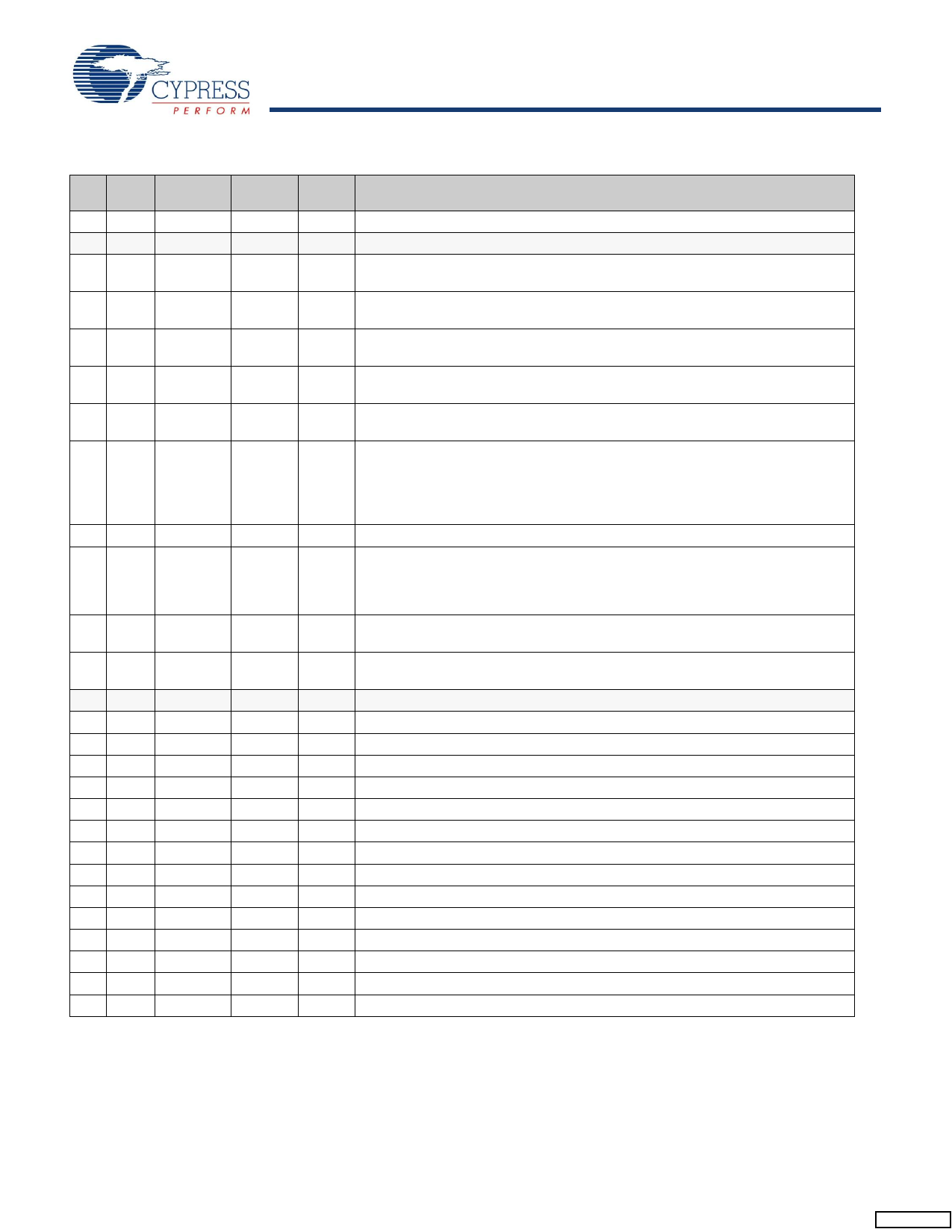

7.0 Register Summary

Table 7-1. SX2 Register Summary

Hex Size Name

Description

D7

D6

D5

D4

D3

D2

D1

D0

Default Access

General Configuration

01 1 IFCONFIG

Interface Configuration

IFCLKSRC 3048MHZ IFCLKOE IFCLKPOL ASYNC STANDBY FLAGD/CS# DISCON 11001001 bbbbbbbb

02 1 FLAGSAB

FIFO FLAGA and FLAGB Assign-

ments

FLAGB3 FLAGB2 FLAGB1 FLAGB0 FLAGA3 FLAGA2 FLAGA1 FLAGA0 00000000 bbbbbbbb

03 1 FLAGSCD

FIFO FLAGC and FLAGD Assign-

ments

FLAGD3 FLAGD2 FLAGD1 FLAGD0 FLAGC3 FLAGC2 FLAGC1 FLAGC0 00000000 bbbbbbbb

04 1 POLAR

FIFO polarities

WUPOL

0

PKTEND SLOE

SLRD

SLWR

EF

FF 00000000 bbbrrrbb

05 1 REVID

Chip Revision

Endpoint Configuration[8]

Major

Major

Major

Major

minor

minor

minor

minor xxxxxxxx rrrrrrrr

06 1 EP2CFG

Endpoint 2 Configuration

VALID

dir

TYPE1

TYPE0

SIZE

STALL

BUF1

BUF0 10100010 bbbbbbbb

07 1 EP4CFG

Endpoint 4 Configuration

VALID

dir

TYPE1

TYPE0

0

STALL

0

0

10100000 bbbbrbrr

08 1 EP6CFG

Endpoint 6 Configuration

VALID

dir

TYPE1

TYPE0

SIZE

STALL

BUF1

BUF0 11100010 bbbbbbbb

09 1 EP8CFG

Endpoint 8 Configuration

VALID

dir

TYPE1

TYPE0

0

STALL

0

0

11100000 bbbbrbrr

0A 1 EP2PKTLENH Endpoint 2 Packet Length H

INFM1 OEP1 ZEROLEN WORD-

0

PL10

PL9

WIDE

PL8 00110010 bbbbbbbb

0B 1 EP2PKTLENL Endpoint 2 Packet Length L (IN only) PL7

PL6

PL5

PL4

PL3

PL2

PL1

PL0 00000000 bbbbbbbb

0C 1 EP4PKTLENH Endpoint 4 Packet Length H

INFM1 OEP1 ZEROLEN WORD-

0

0

PL9

PL8 00110010 bbbbbbbb

WIDE

0D 1 EP4PKTLENL Endpoint 4 Packet Length L (IN only) PL7

PL6

PL5

PL4

PL3

PL2

PL1

PL0 00000000 bbbbbbbb

0E 1 EP6PKTLENH Endpoint 6 Packet Length H

INFM1 OEP1 ZEROLEN WORD-

0

PL10

PL9

WIDE

PL8 00110010 bbbbbbbb

0F 1 EP6PKTLENL Endpoint 6 Packet Length L (IN only) PL7

PL6

PL5

PL4

PL3

PL2

PL1

PL0 00000000 bbbbbbbb

10 1 EP8PKTLENH Endpoint 8 Packet Length H

INFM1 OEP1 ZEROLEN WORD-

0

0

PL9

PL8 00110010 bbbbbbbb

WIDE

11 1 EP8PKTLENL Endpoint 8 Packet Length L (IN only) PL7

PL6

PL5

PL4

PL3

PL2

PL1

PL0 00000000 bbbbbbbb

12 1 EP2PFH

EP2 Programmable Flag H

DECIS PKTSTAT IN: PKTS[2] IN: PKTS[1] IN: PKTS[0]

0

OUT:PFC12 OUT:PFC11 OUT:PFC10

PFC9

PFC8 10001000 bbbbbbbb

13 1 EP2PFL

EP2 Programmable Flag L

PFC7 PFC6

PFC5

PFC4

PFC3

PFC2

PFC1

PFC0 00000000 bbbbbbbb

14 1 EP4PFH

EP4 Programmable Flag H

DECIS PKTSTAT

0

IN: PKTS[1] IN: PKTS[0]

0

OUT:PFC10 OUT:PFC9

0

PFC8 10001000 bbbbbbbb

15 1 EP4PFL

EP4 Programmable Flag L

PFC7 PFC6

PFC5

PFC4

PFC3

PFC2

PFC1

PFC0 00000000 bbbbbbbb

16 1 EP6PFH

EP6 Programmable Flag H

DECIS PKTSTAT IN: PKTS[2] IN: PKTS[1] IN: PKTS[0]

0

OUT:PFC12 OUT:PFC11 OUT:PFC10

PFC9

PFC8 00001000 bbbbbbbb

17 1 EP6PFL

EP6 Programmable Flag L

PFC7 PFC6

PFC5

PFC4

PFC3

PFC2

PFC1

PFC0 00000000 bbbbbbbb

18 1 EP8PFH

EP8 Programmable Flag H

DECIS PKTSTAT

0

IN: PKTS[1] IN: PKTS[0]

0

OUT:PFC10 OUT:PFC9

0

PFC8 00001000 bbbbbbbb

19 1 EP8PFL

EP8 Programmable Flag L

PFC7 PFC6

PFC5

PFC4

PFC3

PFC2

PFC1

PFC0 00000000 bbbbbbbb

1A 1 EP2ISOINPKTS EP2 (if ISO) IN Packets per frame (1-3) 0

0

0

0

0

0

INPPF1

INPPF0 00000001 bbbbbbbb

1B 1 EP4ISOINPKTS EP4 (if ISO) IN Packets per frame (1-3) 0

0

0

0

0

0

INPPF1

INPPF0 00000001 bbbbbbbb

1C 1 EP6ISOINPKTS EP6 (if ISO) IN Packets per frame (1-3) 0

0

0

0

0

0

INPPF1

INPPF0 00000001 bbbbbbbb

1D 1 EP8ISOINPKTS EP8 (if ISO) IN Packets per frame (1-3) 0

0

0

0

0

0

INPPF1

INPPF0 00000001 bbbbbbbb

FLAGS

1E 1 EP24FLAGS Endpoints 2,4 FIFO Flags

0

EP4PF EP4EF EP4FF

0

EP2PF

EP2EF

EP2FF 00100010 rrrrrrrr

1F 1 EP68FLAGS Endpoints 6,8 FIFO Flags

INPKTEND/FLUSH[9]

0

EP8PF EP8EF EP8FF

0

EP6PF

EP6EF

EP6FF 01100110 rrrrrrrr

20 1 INPK-

Force Packet End / Flush FIFOs

FIFO8 FIFO6 FIFO4

FIFO2

EP3

EP2

EP1

EP0 00000000 wwwwww-

TEND/FLUSH

ww

USB Configuration

2A 1 USBFRAMEH USB Frame count H

0

0

0

0

0

FC10

FC9

FC8 xxxxxxxx rrrrrrrr

2B 1 USBFRAMEL USB Frame count L

FC7

FC6

FC5

FC4

FC3

FC2

FC1

FC0 xxxxxxxx rrrrrrrr

2C 1 MICROFRAME Microframe count, 0-7

0

0

0

0

0

MF2

MF1

MF0 xxxxxxxx rrrrrrrr

2D 1 FNADDR

USB Function address

HSGRANT FA6

FA5

FA4

FA3

FA2

FA1

FA0 00000000 rrrrrrrr

Interrupts

2E 1 INTENABLE Interrupt Enable

SETUP EP0BUF FLAGS

1

1

ENUMOK BUSACTIVITY READY 11111111 bbbbbbbb

Descriptor

30 500 DESC

Descriptor RAM

d7

d6

d5

d4

d3

d2

d1

d0

xxxxxxxx wwwwww-

ww

Endpoint 0

31 64 EP0BUF

Endpoint 0 Buffer

d7

d6

d5

d4

d3

d2

d1

d0

xxxxxxxx bbbbbbbb

32 8/1 SETUP

Endpoint 0 Set-up Data / Stall

d7

d6

d5

d4

d3

d2

d1

d0

xxxxxxxx bbbbbbbb

33 1 EP0BC

Endpoint 0 Byte Count

d7

d6

d5

d4

d3

d2

d1

d0

xxxxxxxx bbbbbbbb

Un-Indexed Register control

3A 1

Un-Indexed Register Low Byte pointer a7

a6

a5

a4

a3

a2

a1

a0

3B 1

Un-Indexed Register High Byte point- a7

a6

a5

a4

a3

a2

a1

a0

er

3C 1

Un-Indexed Register Data

d7

d6

d5

d4

d3

d2

d1

d0

Address Un-Indexed Registers in XDATA Space

0xE609 FIFOPINPOLAR FIFO Interface Pins Polarity

0

0

PKTEND SLOE

SLRD

SLWR

EF

FF 00000000 rrbbbbbb

0xE683 TOGCTL

Data Toggle Control

Q

S

R

IO

EP3

EP2

EP1

EP0 xxxxxxxx rbbbbbbb

Notes:

8. Please note that the SX2 was not designed to support dynamic modification of these endpoint configuration registers. If your applications need the ability to

change endpoint configurations after the device has already enumerated with a specific configuration, please expect some delay in being able to access the

FIFOs after changing the configuration. For example, after writing to EP2PKTLENH, you must wait for at least 35 us measured from the time the READY signal

is asserted before writing to the FIFO. This delay time varies for different registers and is not characterized, because the SX2 was not designed for this dynamic

change of endpoint configuration registers.

9. Please note that the SX2 was not designed to support dynamic modification of the INPKTEND/FLUSH register. If your applications need the ability to change

endpoint configurations or access the INPKTEND register after the device has already enumerated with a specific configuration, please expect some delay in

being able to access the FIFOs after changing this register. After writing to INPKTEND/FLUSH, you must wait for at least 85 us measured from the time the

READY signal is asserted before writing to the FIFO. This delay time varies for different registers and is not characterized, because the SX2 was not designed

for this dynamic change of endpoint configuration registers

Document #: 38-08013 Rev. *E

Page 14 of 42