DS2188S(1998) Просмотр технического описания (PDF) - Dallas Semiconductor -> Maxim Integrated

Номер в каталоге

Компоненты Описание

производитель

DS2188S Datasheet PDF : 11 Pages

| |||

DS2188

DS2188

T1/CEPT Jitter Attenuator

FEATURES

• Attenuates clock and data jitter present in T1 or CEPT

lines

• Meets the jitter attenuation templates outlined in

TR62411, TR–TSY–000170, G.735, and G.742

• Only one external component required; either a 6.176

MHz (T1) or 8.192 MHz (CEPT) crystal

• Selectable buffer size of 128 or 32 bits

• Jitter attenuation is easily disabled

• Single +5V supply; low–power CMOS technology

• Available in 16–pin DIP and 16–pin SOIC (DS2188S)

• Companion to the DS2186 Transmit Line and

DS2187 Receive Line Interfaces

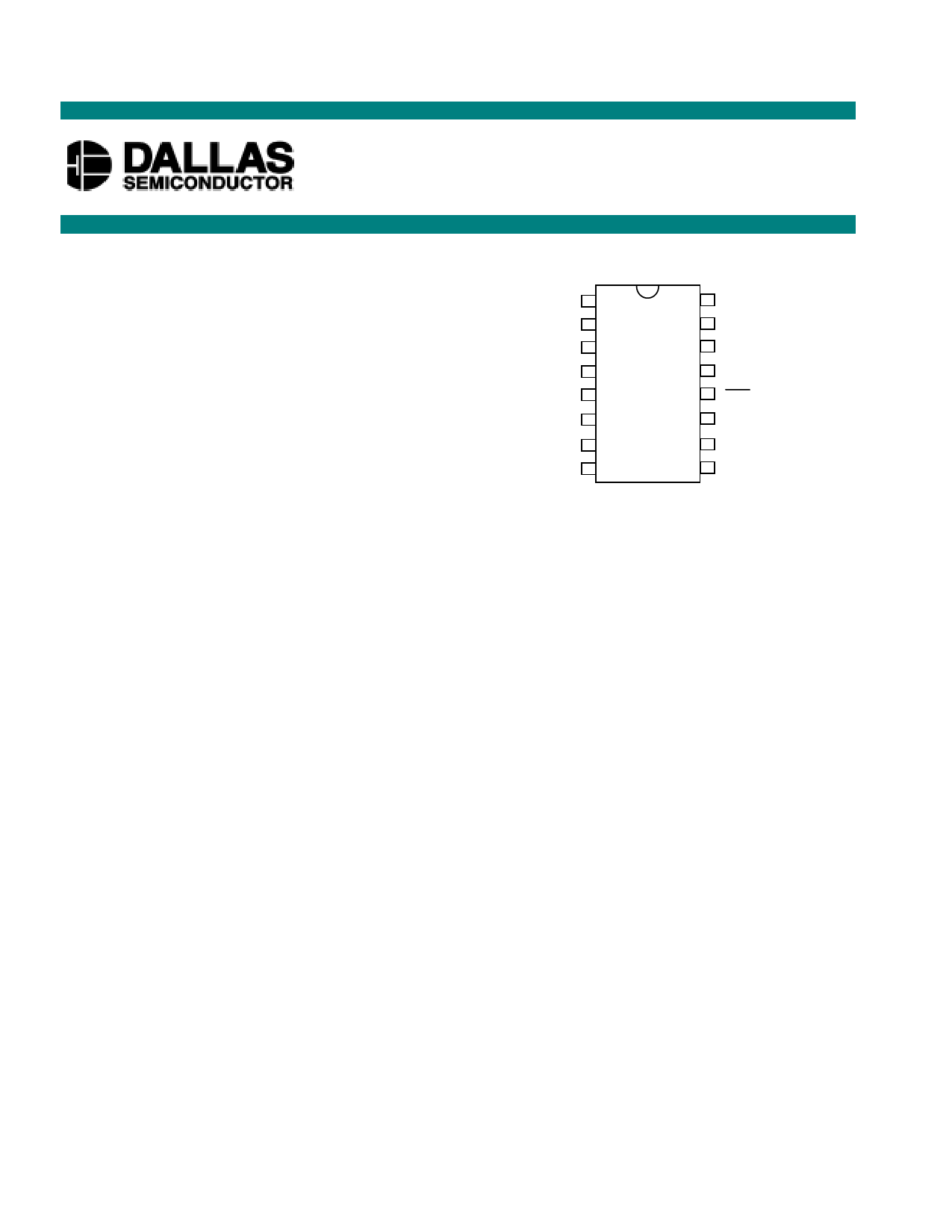

PIN ASSIGNMENT

DJA 1

RPOS 2

RNEG 3

RCLK 4

BDS 5

TEST 6

XTAL OUT 7

VSS 8

16 VDD

15 RRPOS

14 RRNEG

13 RRCLK

12 RST

11 BL

10 XTAL2

9 XTAL1

16–PIN DIP/SOIC

DESCRIPTION

The DS2188 T1/CEPT Jitter Attenuator Chip contains a

128 X 2–bit buffer which, in conjunction with an external

4X crystal, is used to attenuate the incoming jitter pres-

ent in clock and data. The device meets all of the latest

applicable specifications including those outlined in TR

62411 (Accunet* T1.5 Service Description and Interface

Specifications, December 1990), TR–TSY–000170

(Digital Cross–Connect System Requirements and Ob-

jectives, November 1985), and the CCITT Recommen-

dations G.735 and G.742. The DS2188 is compatible

with the DS2180A T1/ISDN Primary Rate Transceiver

and DS2181A CEPT Transceiver and it is the compan-

ion to the DS2187 T1/CEPT Receive Line Interface and

DS2186 T1/CEPT Transmit Line Interface. It can also

be used in conjunction with the DS2190 T1 Network In-

terface Unit.

* Service mark of AT&T Communications

022798 1/11