IT8502F Просмотр технического описания (PDF) - ITE Tech. INC.

Номер в каталоге

Компоненты Описание

производитель

IT8502F Datasheet PDF : 398 Pages

| |||

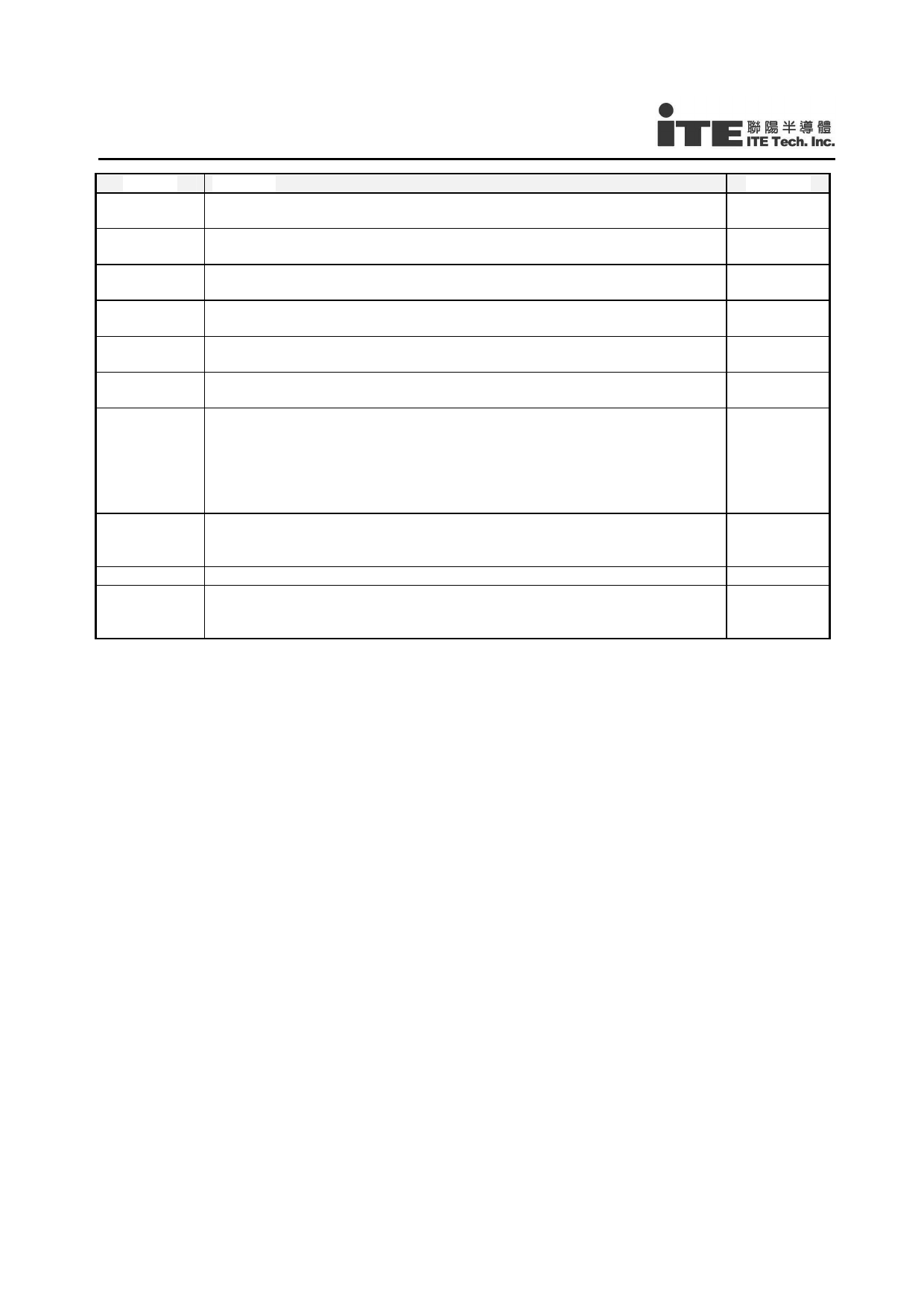

IT8502E/F/G

Section

7

7

7

7

7

7

7

7

7

6, 7

Revision

7.7.4.1 Host Status Register (HOSTA)

Added bit 6, 5 and 2.

7.7.4.11 SMBus Pin Control Register (SMBPCTL)

Added bit 3.

7.7.4.18 Slave Interface Select Register (SLVISELR)

Newly added register.

7.14.4.8 External Timer 2 Counter High Byte 2 (ET2CNTLH2R)

External Timer 2 changed from 16-bit to 24-bit.

7.14.4.9External Timer/WDT Control Register (ETWCTRL)

Added bits to make EWDT be stopped.

Errata:

7.15.4.10Reset Control DMM (RSTDMMC)

7.18.5.3SPI Control Register 2 (SPICTRL2)

Added bit 7-3.

7.18.5.4SPI Start and End Status Register (SPISTS)

Added bit 7-6.

7.18.5.5 SPI Control Register 3 (SPICTRL3)

Newly added register.

7.11.4.7 PWM Polarity Register (PWMPOL)

7.12.4.2 Group Clock Source and Mode Select Register (GCSMS)

6.14 MHz can be available if PLLFREQ == 0011b

7.5.3.1 General Control Register (GCR)

6.2.2.4 Chip Version (CHIPVER)

7.15.4.3 Chip Version (ECHIPVER)

Version registers were revised.

Page No.

232

235

237

295

296

302

316

316

317

266

280

193

45

299

www.ite.com.tw

B

IT8502E/F/G V0.7.7